Users Manual

# 32bit RISC Microprocessor TX39 family

# TMPR3904F

Rev.2.0

Jan. 12. 1998

| 1 | INTR | RODUCTION                                  | 1  |

|---|------|--------------------------------------------|----|

|   | 1.1  | Overview                                   | 1  |

|   | 1.2  | Notation used in this manual               | 2  |

|   | 1.3  | Kind of accessing by the TX3904            | 3  |

|   | 1.4  | Precautions in the TMPR3904F specification | 4  |

| 2 | FEA  | TURES                                      | 7  |

| 3 | CON  | IFIGURATION                                | 9  |

| 4 | PINS | 5                                          | 11 |

|   | 4.1  | Positions of Pins                          | 11 |

|   | 4.2  | Functions of Pins                          | 13 |

| 5 | ADD  | RESS MAPS                                  | 17 |

|   | 5.1  | Memory Map                                 | 17 |

|   | 5.2  | Register Map                               | 18 |

|   | 5.3  | Chip Configuration Register                | 21 |

|   |      | 5.3.1 DMA transfer of SIO                  | 21 |

|   |      | 5.3.2 PIO2 and PIO1                        | 22 |

|   |      | 5.3.3 Error processing                     | 23 |

|   |      | 5.3.4 Connection of external bus master    | 24 |

|   |      | 5.3.5 INT[7:0] active status clear         | 24 |

|   |      | 5.3.6 INT[7:0] active status set-up        | 25 |

| 6 |      | СК                                         |    |

|   | 6.1  | Clock Generator                            |    |

|   | 6.2  | Operation Modes of TX3904                  |    |

|   |      | 6.2.1 Normal mode                          |    |

|   |      | 6.2.2 Halt mode                            |    |

|   |      | 6.2.3 Doze mode                            |    |

|   |      | 6.2.4 RF (Reduced Frequency) mode          |    |

|   | 6.3  | Status Shifting                            |    |

|   | 6.4  | Operations of each block in the each modes |    |

| 7 |      | OPERATIONS                                 |    |

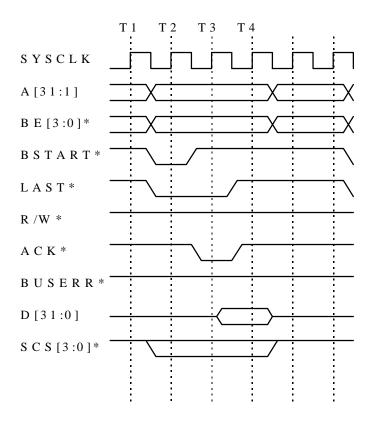

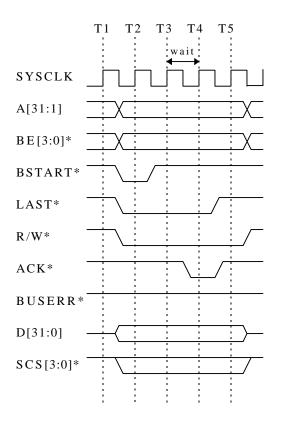

|   | 7.1  | Basic Bus Operations                       |    |

|   |      | 7.1.1 System chip select                   |    |

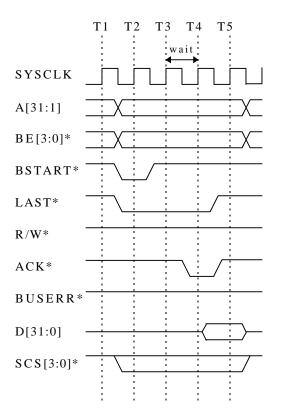

|   |      | 7.1.2 Single read operation                |    |

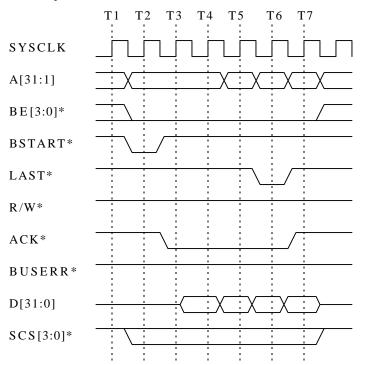

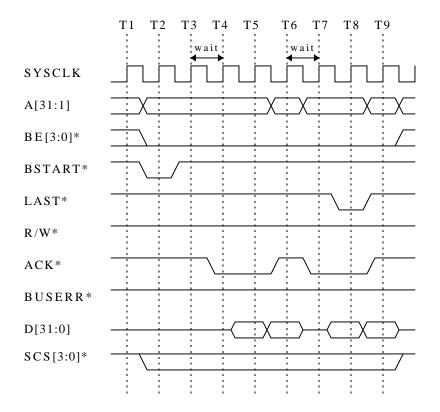

|   |      | 7.1.3 Burst read operation                 |    |

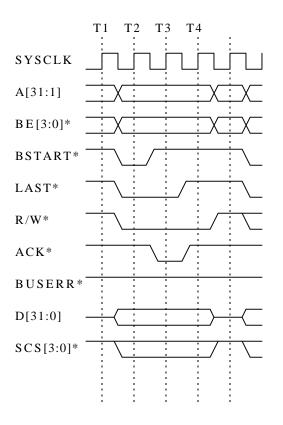

|   |      | 7.1.4 Single write operation               |    |

|   | 7.2  | Bus Error                                  |    |

|   |      | 7.2.1 BUSERR* signal                       | 41 |

|   |     | 7.2.2 Absence register access                  | 41 |

|---|-----|------------------------------------------------|----|

|   |     | 7.2.3 Time-out error                           | 41 |

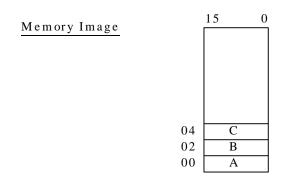

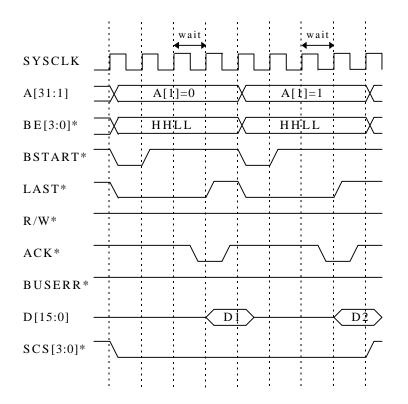

|   | 7.3 | 16-bit Bus Mode                                | 43 |

|   | 7.4 | Half Speed Bus Mode                            | 45 |

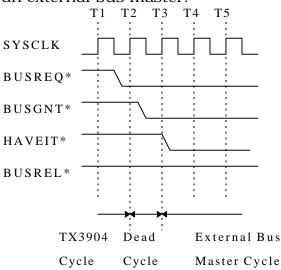

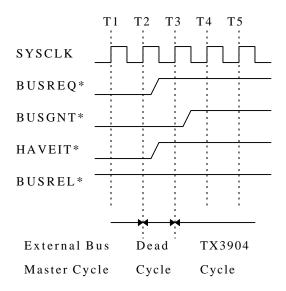

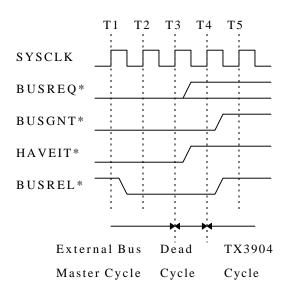

|   | 7.5 | Bus Arbitration                                | 46 |

|   |     | 7.5.1 Bus ownership granted                    | 46 |

|   |     | 7.5.2 Release of bus ownership                 | 47 |

|   |     | 7.5.3 Kinds of bus ownership                   |    |

|   |     | 7.5.4 Snoop function                           |    |

|   | 7.6 | Interrupts                                     |    |

|   |     | 7.6.1 INT[7:0]                                 |    |

|   |     | 7.6.2 NMI*                                     |    |

|   | 7.7 | Reset                                          |    |

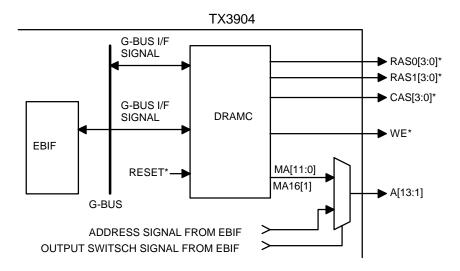

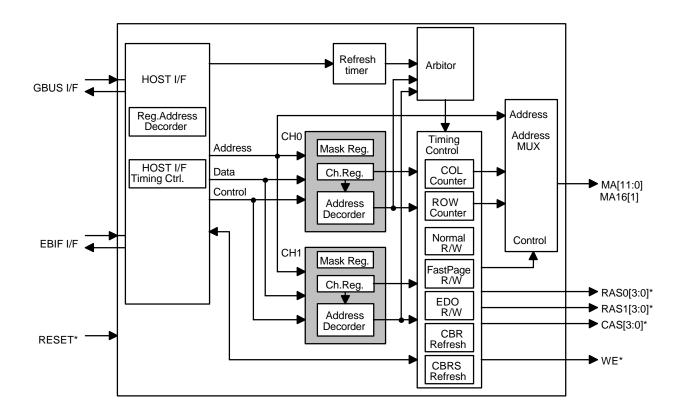

| 8 | DRA | AM CONTROLLER (DRAMC)                          | 51 |

|   | 8.1 | Features                                       | 51 |

|   | 8.2 | Block Diagrams                                 |    |

|   | 8.3 | Registers                                      | 53 |

|   | 8.4 | Explanations of Registers                      |    |

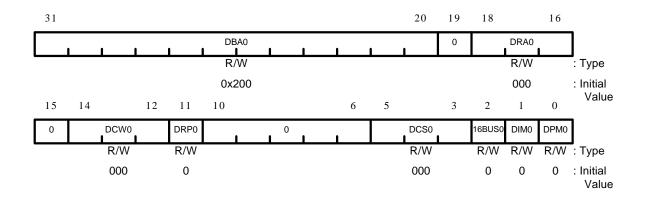

|   |     | 8.4.1 Channel control register 0 (DCCR0)       |    |

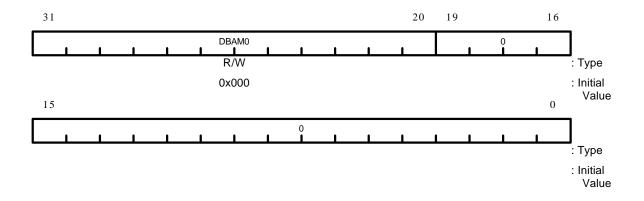

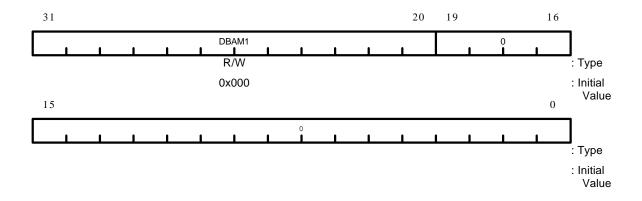

|   |     | 8.4.2 Base address mask register 0 (DBMR0)     | 56 |

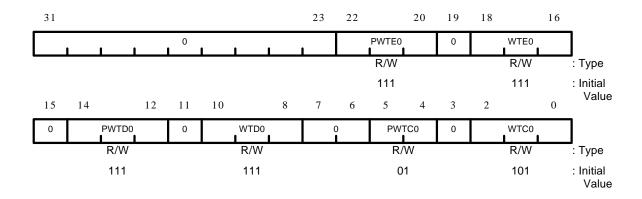

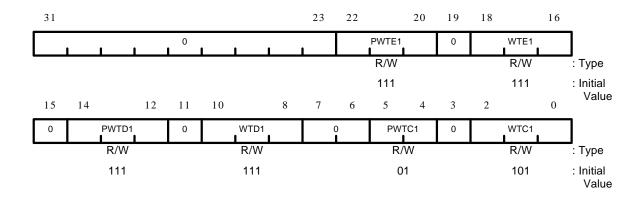

|   |     | 8.4.3 Wait register 0 (DWR0)                   | 57 |

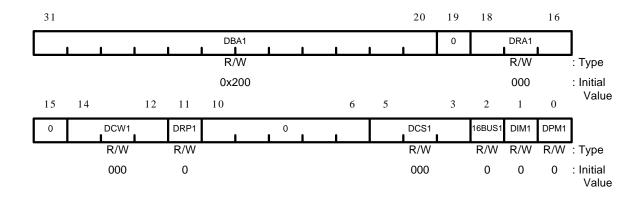

|   |     | 8.4.4 Channel control register 1 (DCCR1)       |    |

|   |     | 8.4.5 Base address mask register 1 (DBMR1)     | 61 |

|   |     | 8.4.6 Wait register 1 (DWR1)                   |    |

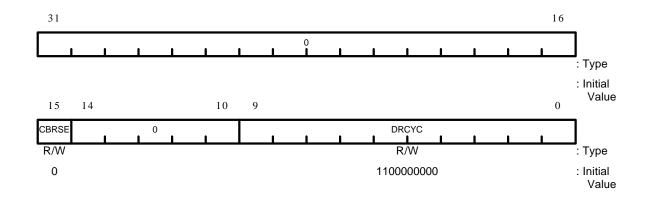

|   |     | 8.4.7 Refresh control register (DREFC)         | 64 |

|   | 8.5 | Operations                                     | 65 |

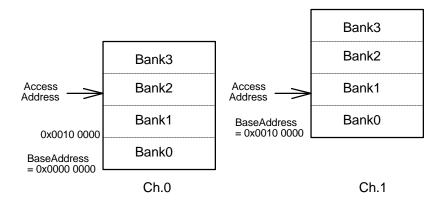

|   |     | 8.5.1 Channel select                           |    |

|   |     | 8.5.2 Address multiplex                        | 66 |

|   |     | 8.5.3 Operation modes                          |    |

|   |     | 8.5.4 32/16-bit static bus sizing              |    |

|   |     | 8.5.5 Support for external bus master          |    |

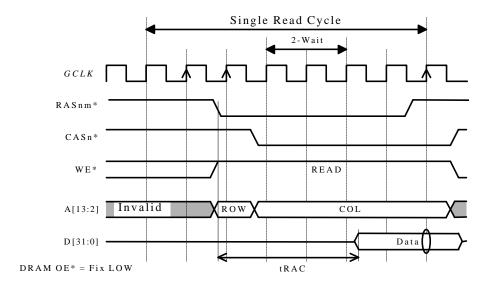

|   |     | 8.5.6 Support for half speed bus               |    |

|   |     | 8.5.7 Page mode support and page hit detection |    |

|   |     | 8.5.8 Column address counter                   | 69 |

|   |     | 8.5.9 Timing control                           | 69 |

|   |     | 8.5.10 Refresh timing                          | 69 |

|   |     | 8.5.11 Arbiter                                 | 70 |

|   |     |                                                |    |

|   |     | 8.5.12 Operations at the time of reset                           | 70   |

|---|-----|------------------------------------------------------------------|------|

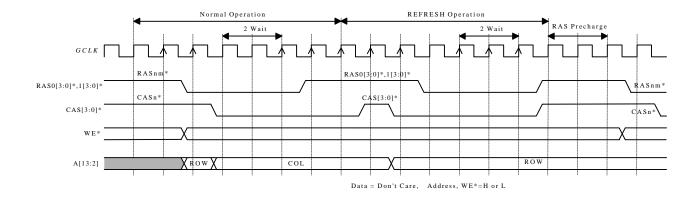

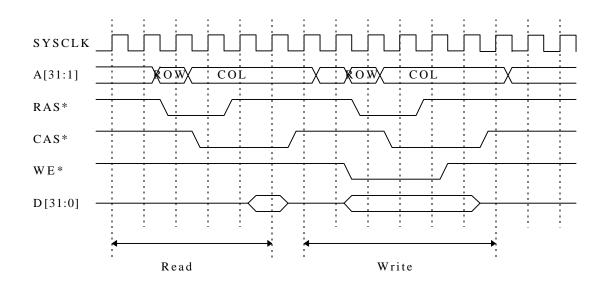

|   | 8.6 | Timing Diagrams                                                  | 71   |

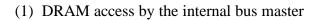

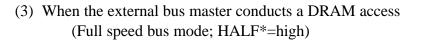

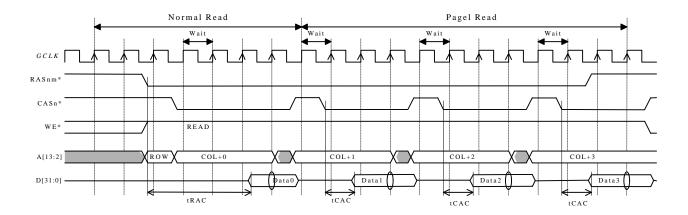

|   |     | 8.6.1 32-bit bus single read operation                           | 71   |

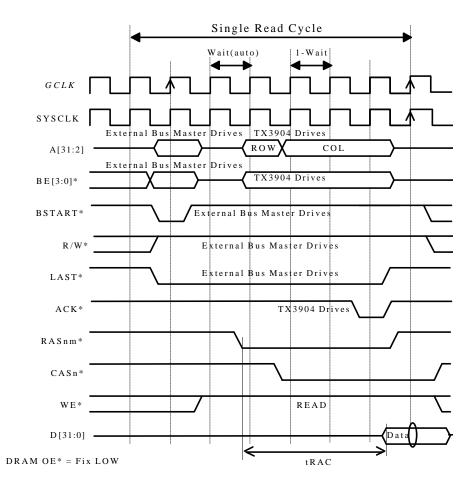

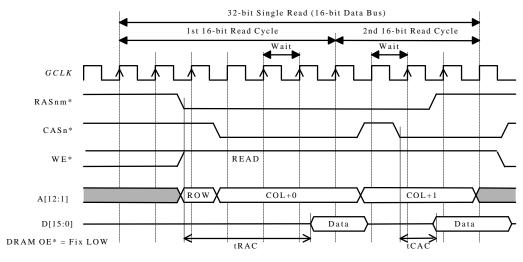

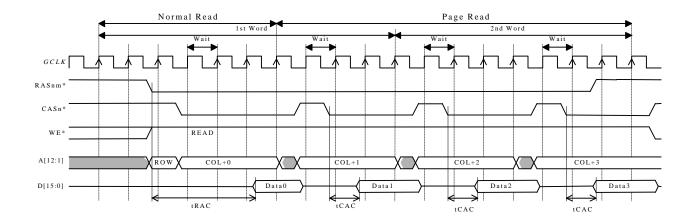

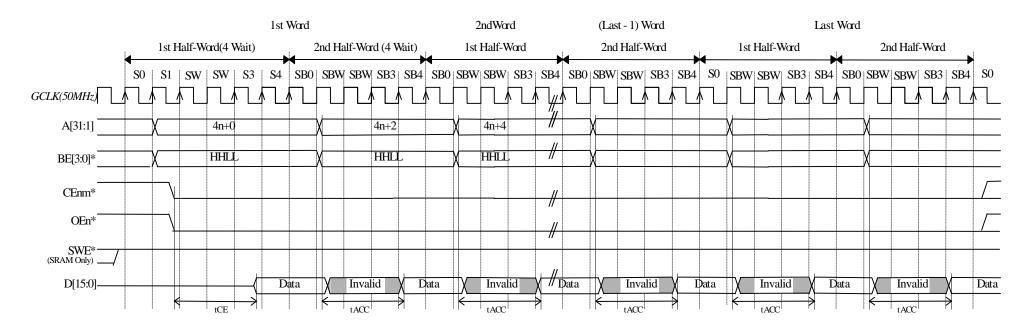

|   |     | 8.6.2 32-bit word single read operation with 16-bit bus          | 74   |

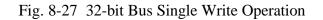

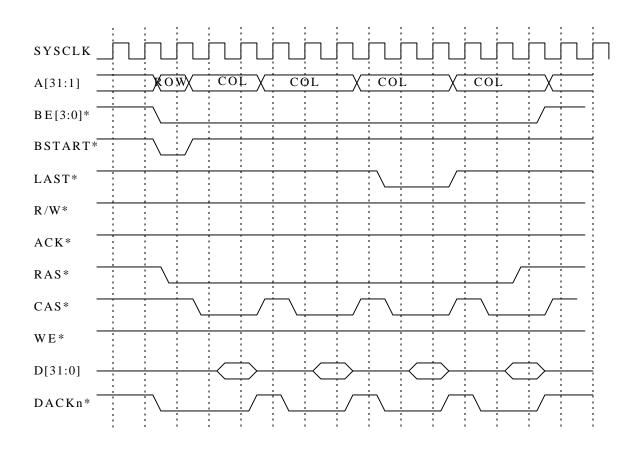

|   |     | 8.6.3 32-bit bus fast page mode read (Burst mode)                | 75   |

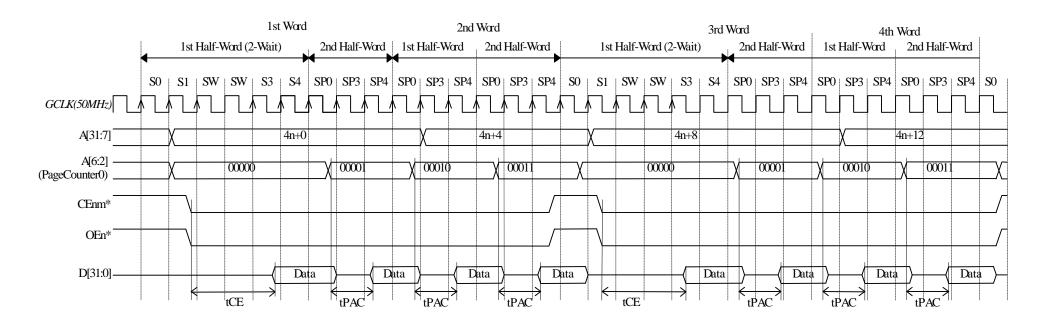

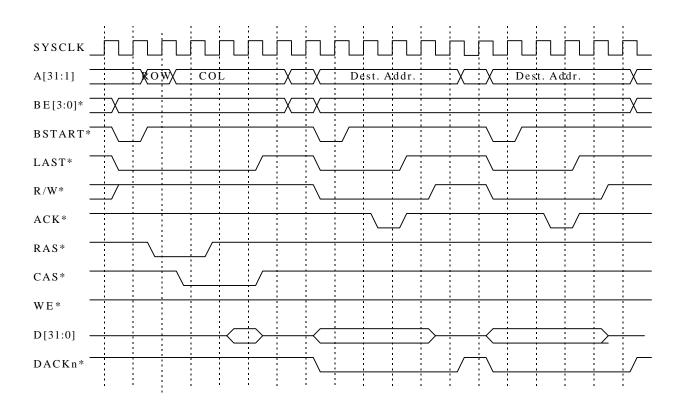

|   |     | 8.6.4 16-bit bus fast page mode word read (Burst read)           | 75   |

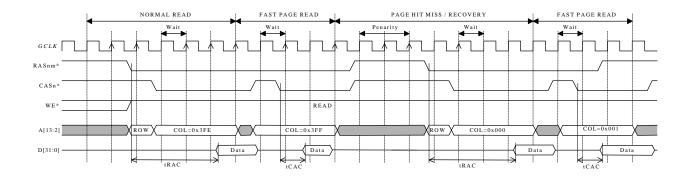

|   |     | 8.6.5 32-bit bus fast page mode read (Burst read) page hit miss  | 76   |

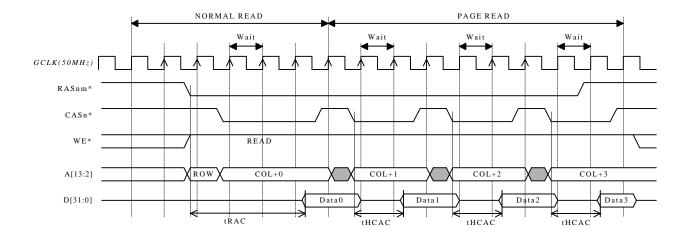

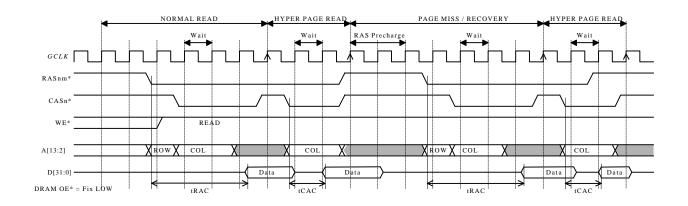

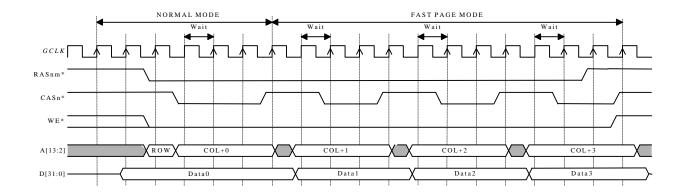

|   |     | 8.6.6 32-bit bus hyper page mode read (Burst read)               | 77   |

|   |     | 8.6.7 32-bit bus hyper page mode read (Page hit miss)            | 77   |

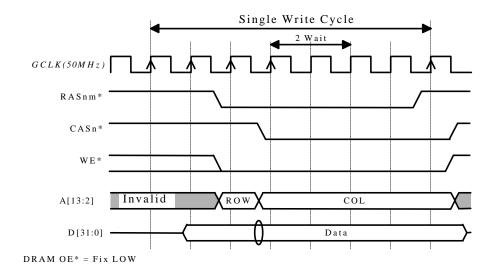

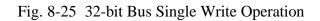

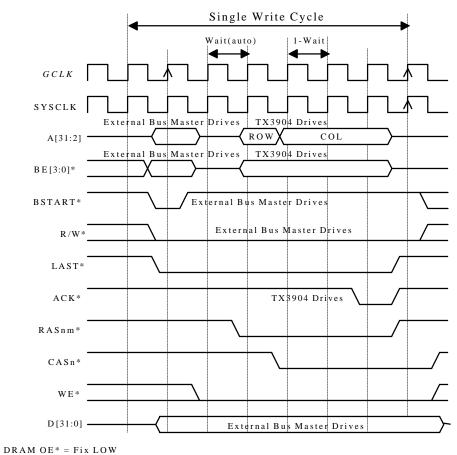

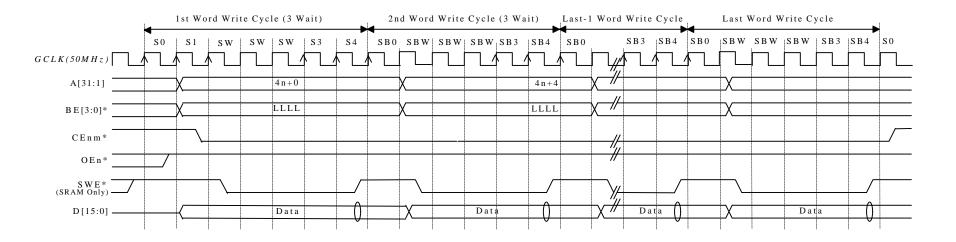

|   |     | 8.6.8 32-bit bus single write (Early write)                      | 78   |

|   |     | 8.6.9 32-bit bus fast page mode write (Early write)              | 81   |

|   |     | 8.6.10 32-bit bus hyper page mode write (Early write)            | 81   |

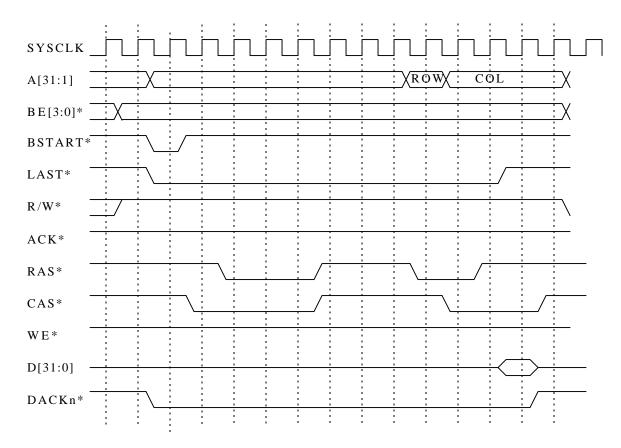

|   |     | 8.6.11 CBR refresh                                               | 82   |

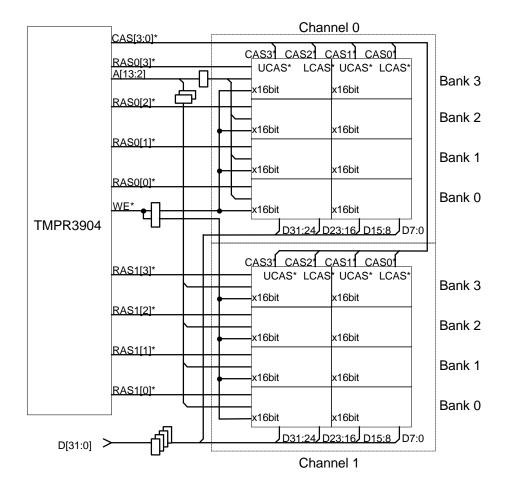

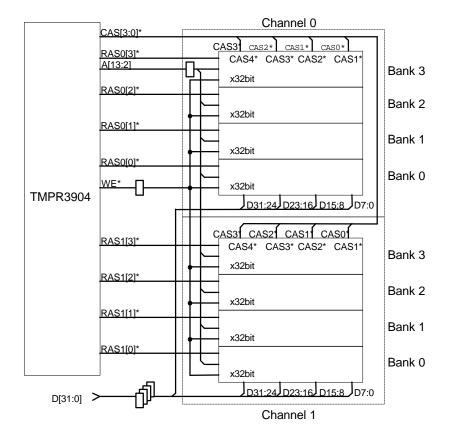

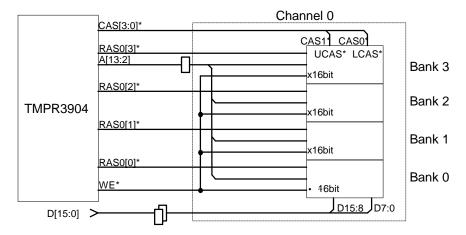

|   | 8.7 | External Circuit Connections                                     | 83   |

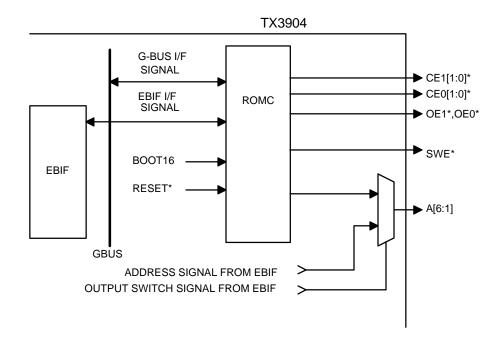

| 9 | ROM | I CONTROLLER (ROMC)                                              | 85   |

|   | 9.1 | Features                                                         | 85   |

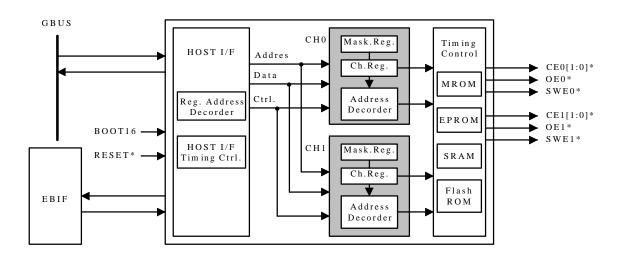

|   | 9.2 | Block Diagrams                                                   | 86   |

|   | 9.3 | Registers                                                        | 87   |

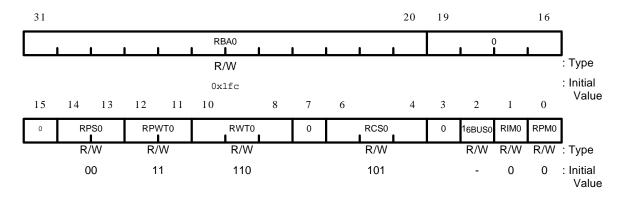

|   |     | 9.3.1 Channel control register 0                                 | 88   |

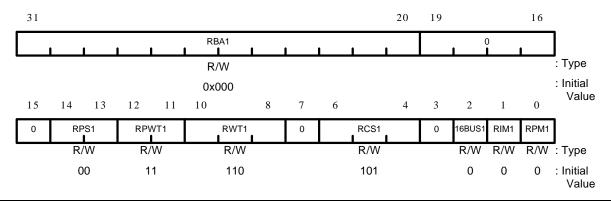

|   |     | 9.3.2 Channel control register 1                                 | 90   |

|   |     | 9.3.3 Base address mask register 0                               | 92   |

|   |     | 9.3.4 Base address mask register 1                               | 93   |

|   | 9.4 | Operations                                                       | 94   |

|   |     | 9.4.1 Channel select                                             | 94   |

|   |     | 9.4.2 Operation Modes                                            | 96   |

|   |     | 9.4.3 32/16-bit Static Bus Sizing                                | 97   |

|   |     | 9.4.4 16-bit Bus Access                                          | 97   |

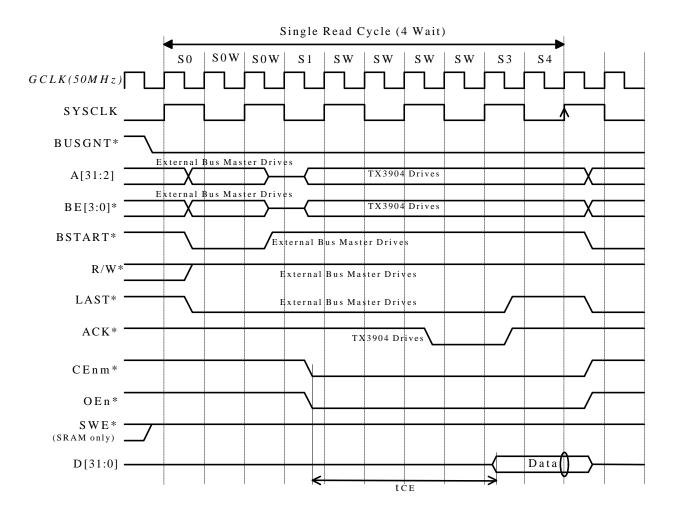

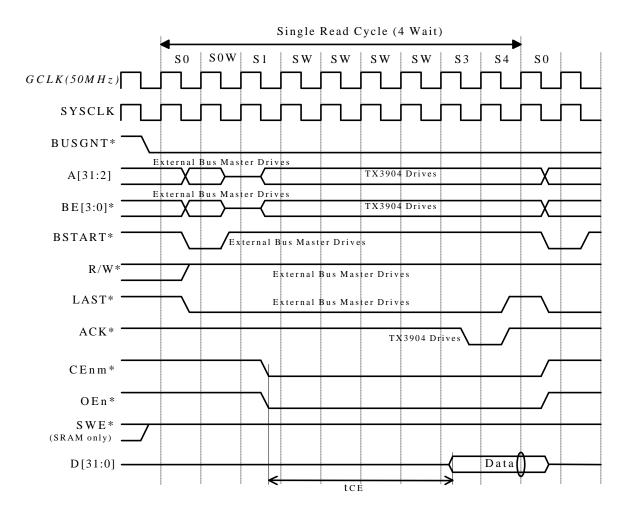

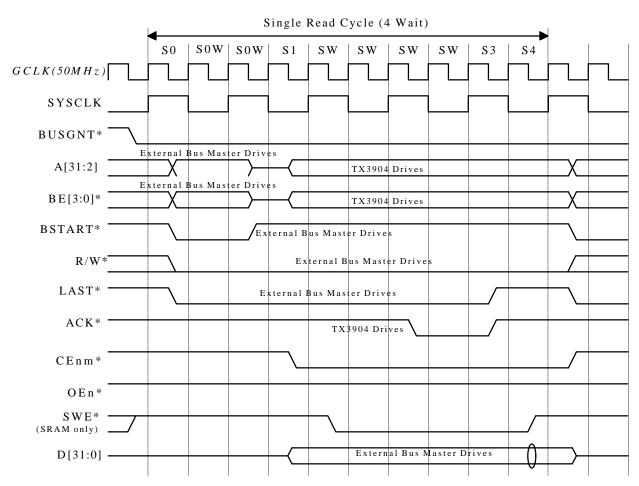

|   |     | 9.4.5 Access by External Bus Master                              | 97   |

|   |     | 9.4.6 Page mode support                                          | 97   |

|   | 9.5 | Timing Diagrams                                                  | 98   |

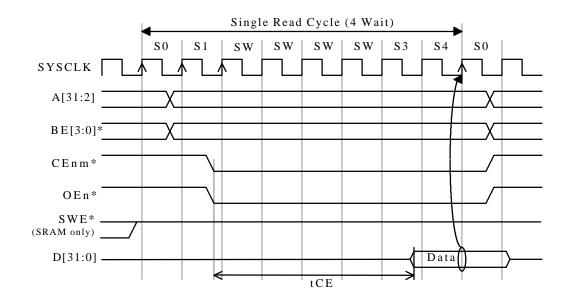

|   |     | 9.5.1 32-bit bus single read operation (ROM/SRAM)                | 98   |

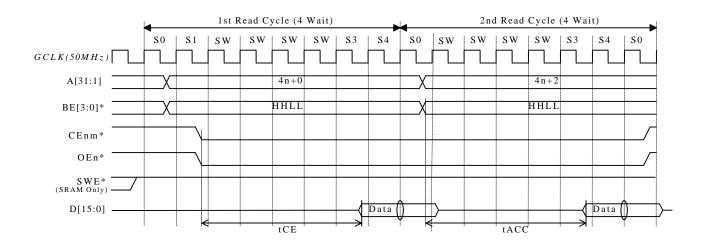

|   |     | 9.5.2 16-bit bus single read (32-bit word) operation (ROM/SRAM)  | .101 |

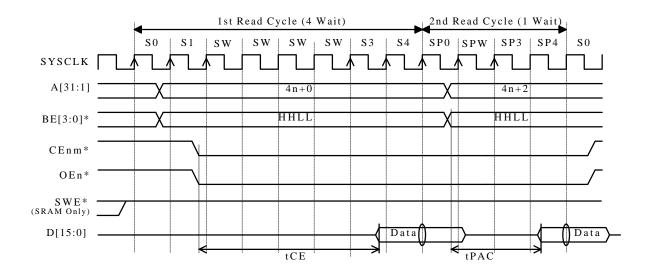

|   |     | 9.5.3 16-bit bus single read (half word) operation (ROM/SRAM)    | .102 |

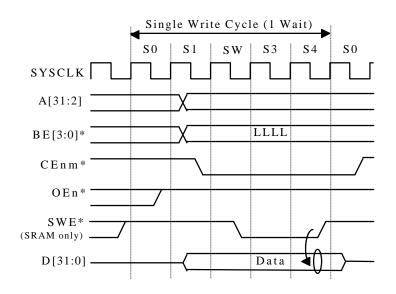

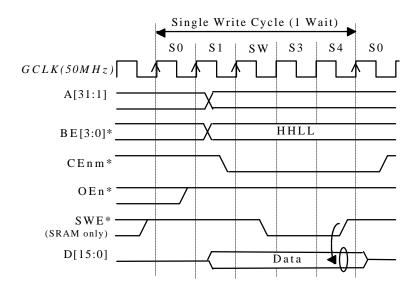

|   |     | 9.5.4 32-bit bus single write operation (SRAM/Flush)             | .102 |

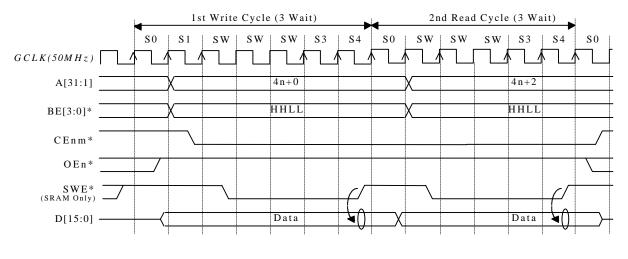

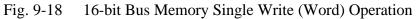

|   |     | 9.5.5 16-bit bus single write (word) operation (SRAM/Flush)      | .104 |

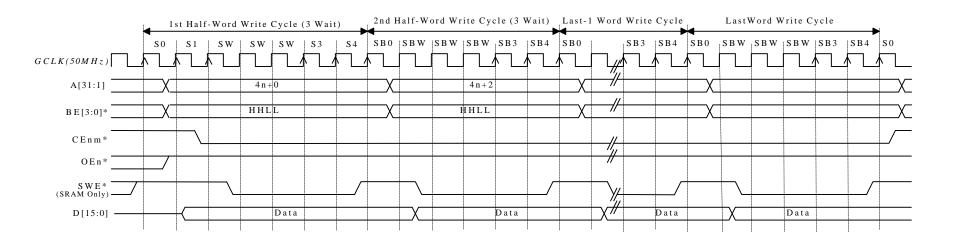

|   |     | 9.5.6 16-bit bus single write (half word) operation (SRAM/Flush) |      |

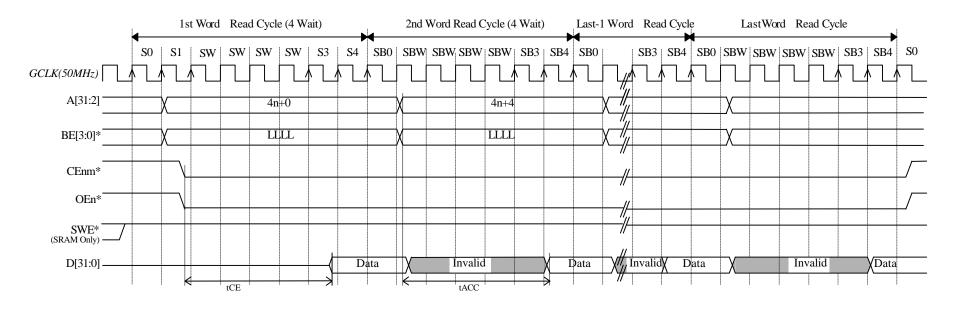

|   |     | 9.5.7 32-bit bus normal mode burst read operation (ROM/SRAM)     | .105 |

|   |     |                                                                  |      |

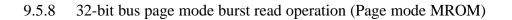

|    |        | 9.5.8 32-bit bus page mode burst read operation (Page mode MROM)          | 106 |

|----|--------|---------------------------------------------------------------------------|-----|

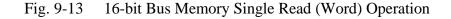

|    |        | 9.5.9 16-bit bus word normal mode burst read operation (ROM/SRAM)         | 107 |

|    |        | 9.5.10 16-bit bus page mode burst read (word) operation (Page mode MROM)  | 108 |

|    |        | 9.5.11 32-bit bus normal mode burst write (SRAM)                          | 109 |

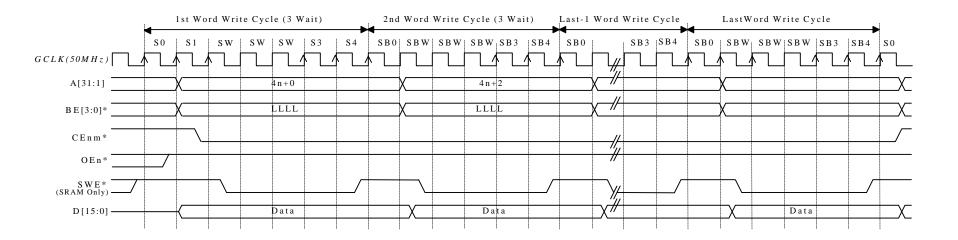

|    |        | 9.5.12 16-bit bus normal mode burst write (word) (SRAM; WE control write) | 110 |

|    |        | 9.5.13 16-bit bus normal mode burst write (half word) (SRAM; WE control)  | 111 |

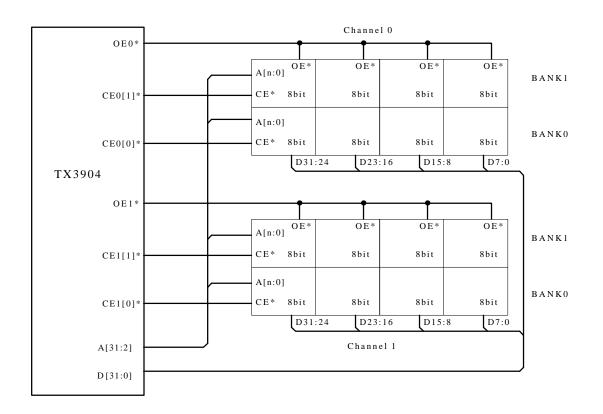

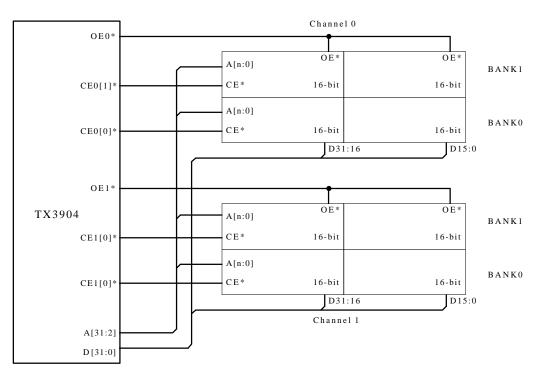

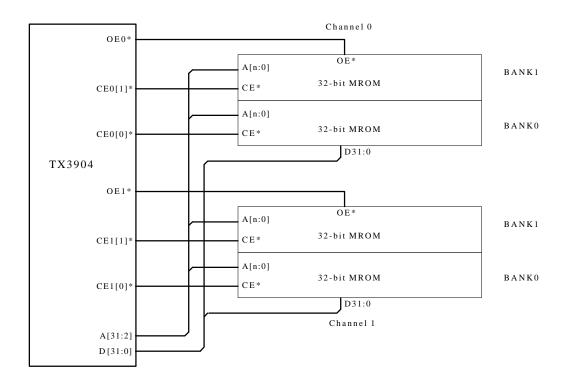

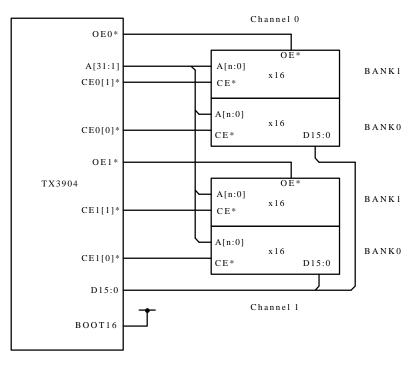

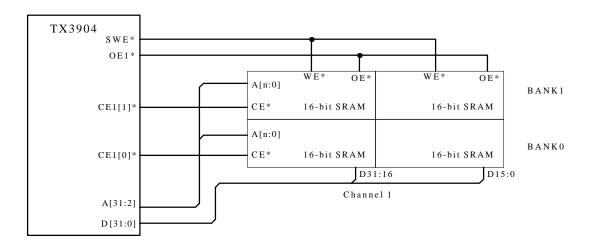

|    | 9.6    | Examples of MROM/EPROM Usage                                              | 112 |

|    | 9.7    | Examples of SRAM Usage                                                    | 114 |

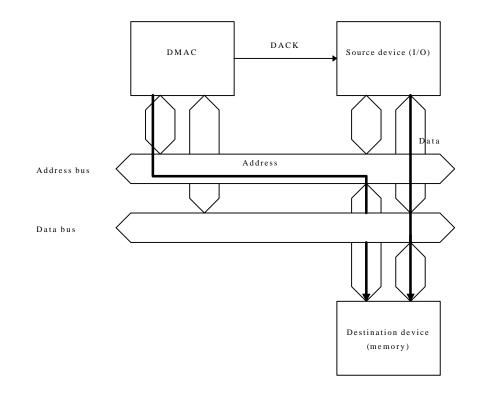

| 10 | DMA    | A CONTROLLER (DMAC)                                                       | 116 |

|    | 10.1   | Features                                                                  | 116 |

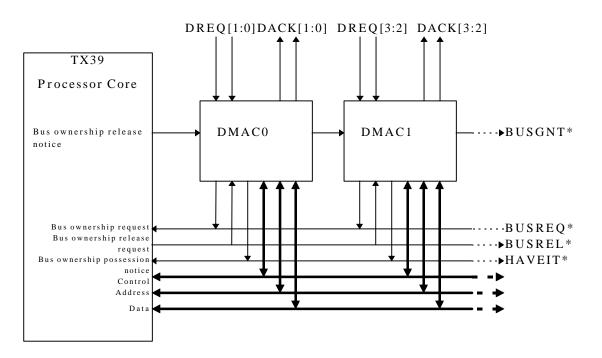

|    | 10.2   | Configuration                                                             | 117 |

|    | 10.2.  | 1 TX3904 internal connection                                              | 117 |

|    | 10.2.2 | 2DMAC internal blocks                                                     | 118 |

|    | 10.2.3 | 3 Priority between modules                                                | 118 |

|    | 10.3   | Registers                                                                 | 120 |

|    |        | 10.3.1 DMA control register (DCR)                                         | 121 |

|    |        | 10.3.2 Channel control register (CCRn)                                    | 122 |

|    |        | 10.3.3 Channel status register (CSRn)                                     | 126 |

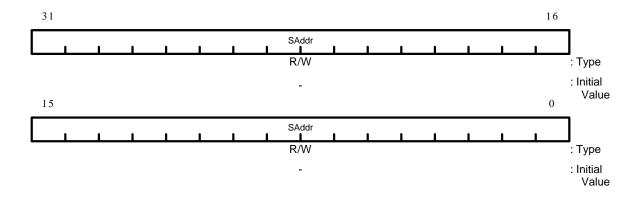

|    |        | 10.3.4 Source address register (SARn)                                     | 129 |

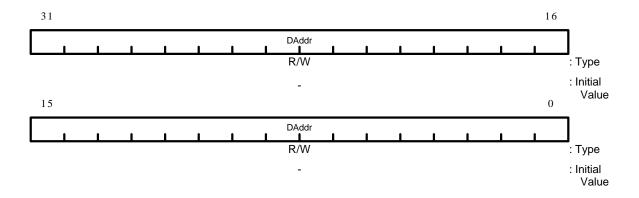

|    |        | 10.3.5 Destination address register (DARn)                                | 130 |

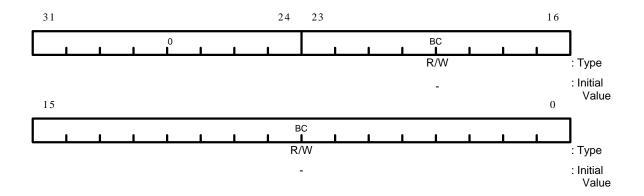

|    |        | 10.3.6 Byte count register (BCR0n)                                        | 131 |

|    |        | 10.3.7 Next byte count register (NCR0/1)                                  | 132 |

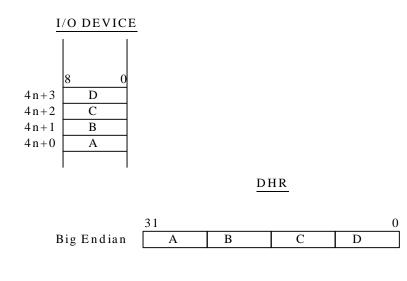

|    |        | 10.3.8 Data holding register (DHR)                                        | 133 |

|    | 10.4   | Functions                                                                 | 134 |

|    |        | 10.4.1 Overview                                                           | 134 |

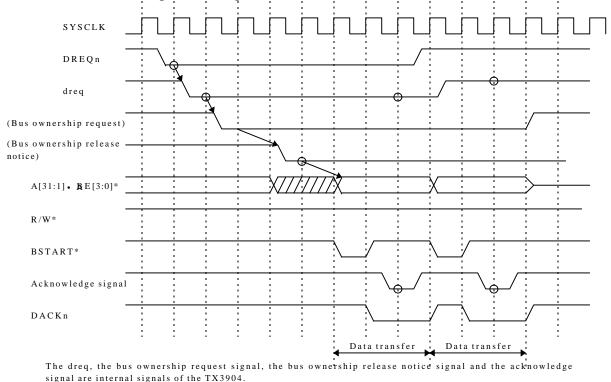

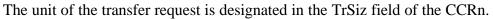

|    |        | 10.4.2 Transfer requests                                                  | 138 |

|    |        | 10.4.3 Address modes                                                      | 142 |

|    |        | 10.4.4 Burst transfer                                                     | 147 |

|    |        | 10.4.5 Continue mode                                                      | 147 |

|    |        | 10.4.6 Channel operation                                                  | 148 |

|    |        | 10.4.7 Endian switch function                                             | 152 |

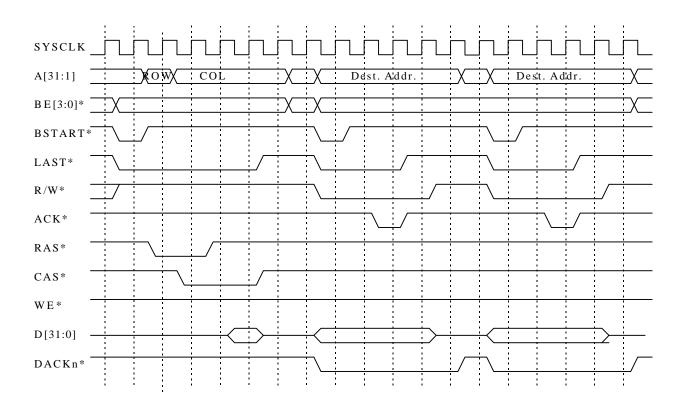

|    | 10.5   | Operations                                                                | 153 |

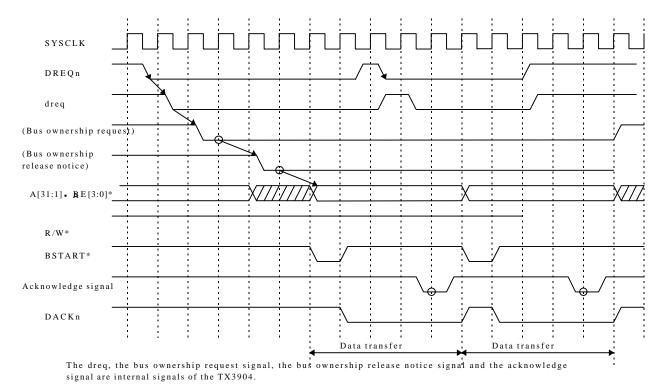

|    |        | 10.5.1 Dual address mode                                                  | 153 |

|    |        | 10.5.2 Single address mode                                                | 156 |

|    |        | 10.5.3 Input of DONE* signal                                              | 159 |

|    |        | 10.5.4 Output of DONE* signal                                             | 160 |

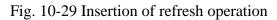

|    |        | 10.5.5 Note for DRAM refresh during DMA                                   | 160 |

|    |        |                                                                           |     |

| 11 | INTE | RRUPTS                                         | 162 |

|----|------|------------------------------------------------|-----|

|    | 11.1 | Features                                       | 162 |

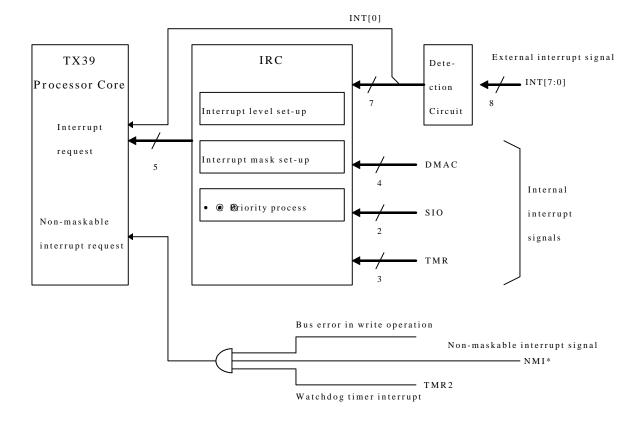

|    | 11.2 | Configuration                                  | 163 |

|    | 11.3 | Functions                                      | 164 |

|    |      | 11.3.1 Interrupt sources                       | 164 |

|    |      | 11.3.2 Interrupt detection                     | 165 |

|    |      | 11.3.3 Interrupt priority arbitration process  | 165 |

|    | 11.4 | Registers                                      | 166 |

|    |      | 11.4.1 Register map                            | 166 |

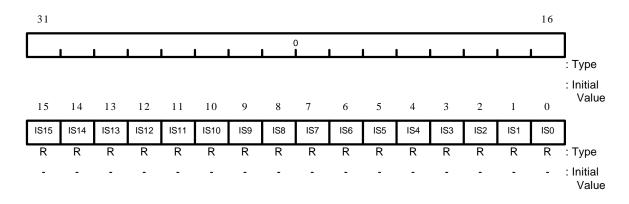

|    |      | 11.4.2 Interrupt status register (ISR)         | 167 |

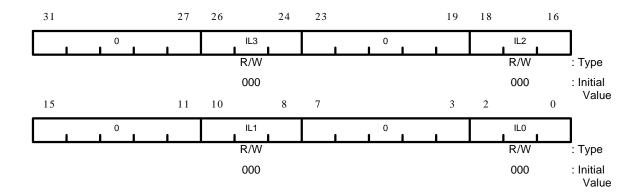

|    |      | 11.4.3 Interrupt level registers (ILR3-ILR0)   | 168 |

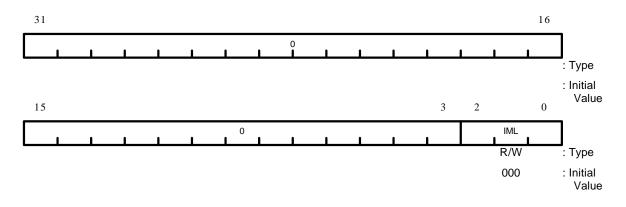

|    |      | 11.4.4 Interrupt mask register (IMR)           | 169 |

| 12 | SERI | AL PORTS (SIO)                                 | 170 |

|    | 12.1 | Features                                       | 170 |

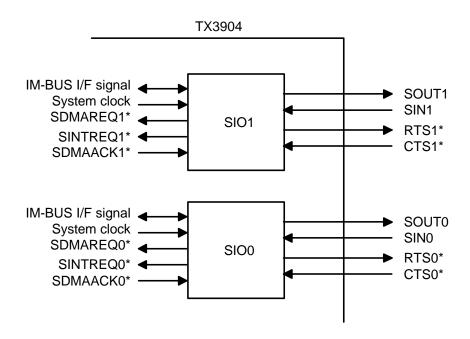

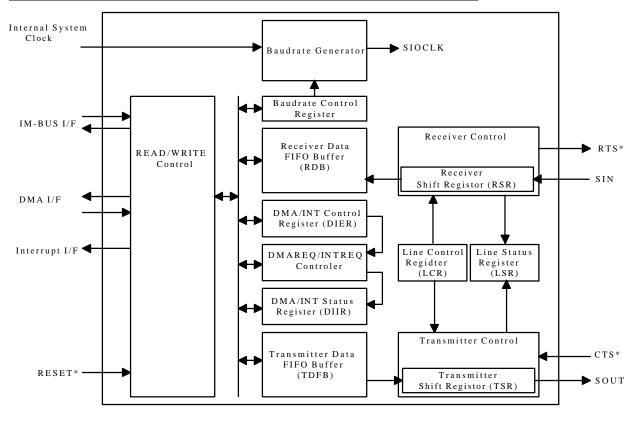

|    | 12.2 | Block Diagrams                                 | 170 |

|    | 12.3 | Registers                                      | 172 |

|    |      | 12.3.1 Line control register (SLCRn)           | 173 |

|    |      | 12.3.2 Line status register (SLSRn)            | 175 |

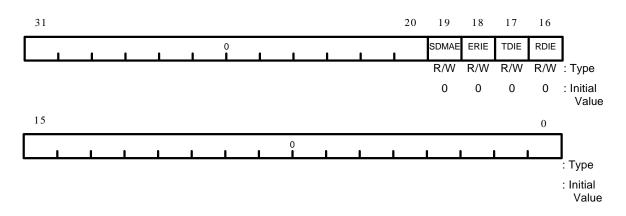

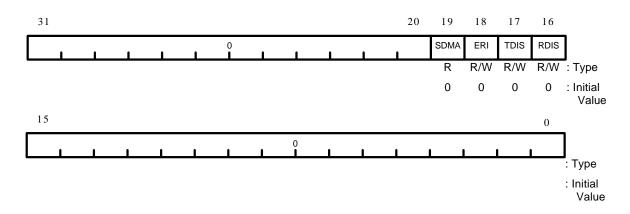

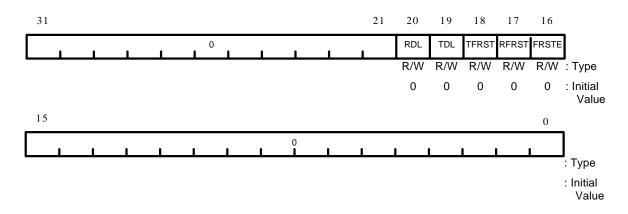

|    |      | 12.3.3 DMA/Interrupt control register (SDICRn) | 176 |

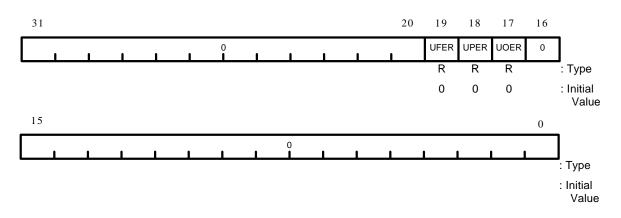

|    |      | 12.3.4 DMA/Interrupt status register (SDISRn)  | 178 |

|    |      | 12.3.5 FIFO control register (SFCRn)           |     |

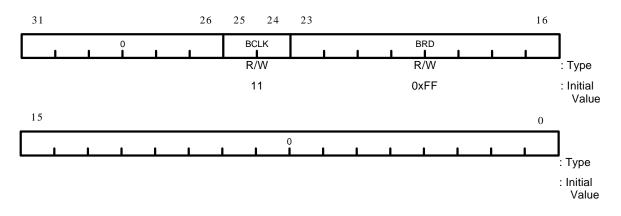

|    |      | 12.3.6 Baudrate control register (SBGRn)       |     |

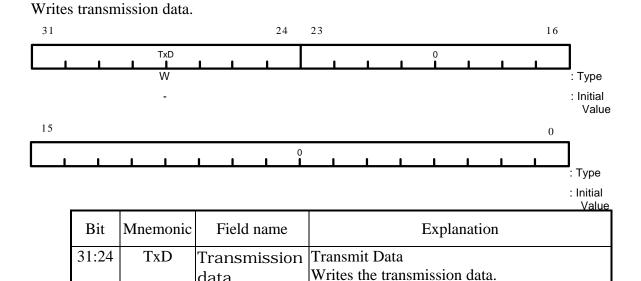

|    |      | 12.3.7 Transmit FIFO buffer (TFIFOn)           |     |

|    |      | 12.3.8 Receive FIFO buffer (SFIFOn)            |     |

|    | 12.4 | Operations                                     |     |

|    |      | 12.4.1 Overview                                |     |

|    |      | 12.4.2 Data format                             |     |

|    |      | 12.4.3 Serial clock generator                  |     |

|    |      | 12.4.4 Baudrate generator                      |     |

|    |      | 12.4.5 Receiver Controller                     |     |

|    |      | 12.4.6 Receiver shift register                 |     |

|    |      | 12.4.7 Receiver read buffer                    |     |

|    |      | 12.4.8 Transmitter controller                  |     |

|    |      | 12.4.9 Transmitter shift register              |     |

|    |      | 12.4.10 Host I/F                               |     |

|    |      | 12.4.11 Hand shake function                    |     |

|    |      | 12.4.12 Parity control                         | 189 |

|    |       | 12.4.13 Error flag                                                                     | 189 |

|----|-------|----------------------------------------------------------------------------------------|-----|

|    |       | 12.4.14 Multi-controller system                                                        |     |

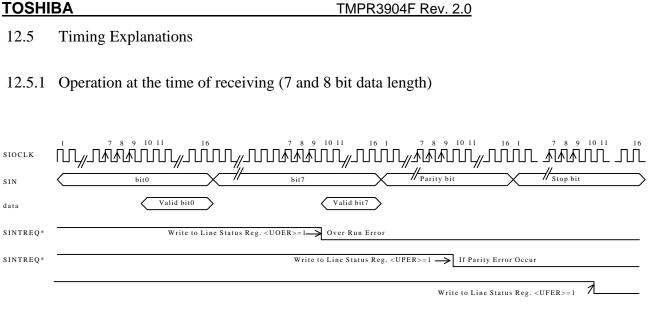

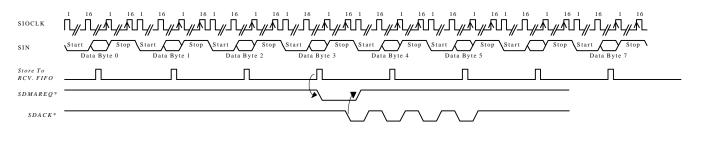

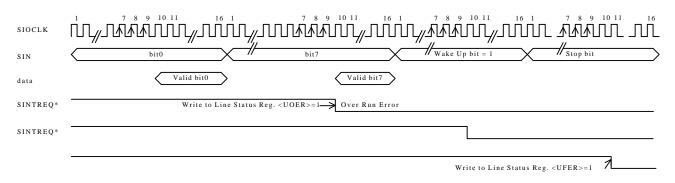

|    | 12.5  | Timing Explanations                                                                    | 191 |

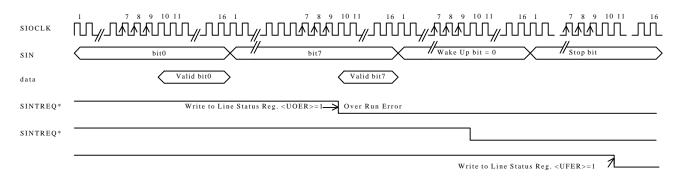

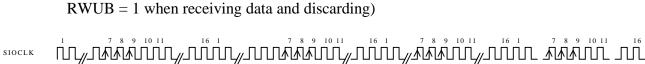

|    |       | 12.5.1 Operation at the time of receiving (7 and 8 bit data length)                    | 191 |

|    |       | 12.5.2 Timing of SDMAREQ*/SMAACK* at the time of DMA I/F (at DMA level 4)              |     |

|    |       | 12.5.3 Operation at the time of receiving (8 and 9 bit length multi-controller system; | 192 |

|    |       | 12.5.4 Operation at the time of receiving (8 and 9 bit length multi-controller system; |     |

|    |       | 12.5.5 Operation at the time of receiving (8 and 9 bit length multi-controller system; | 193 |

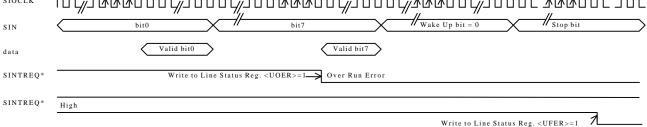

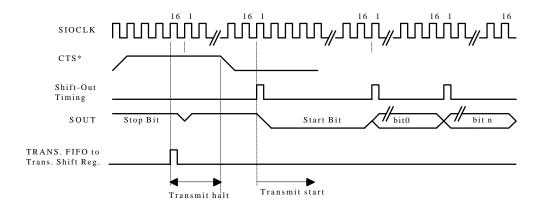

|    |       | 12.5.6 Operation at the time of transmitting                                           | 193 |

|    |       | 12.5.7 Transmit halt timing by CTS*                                                    | 194 |

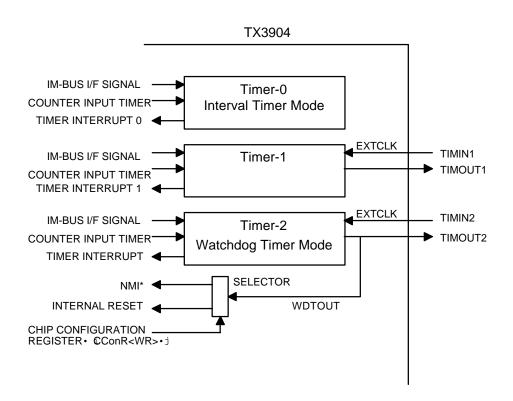

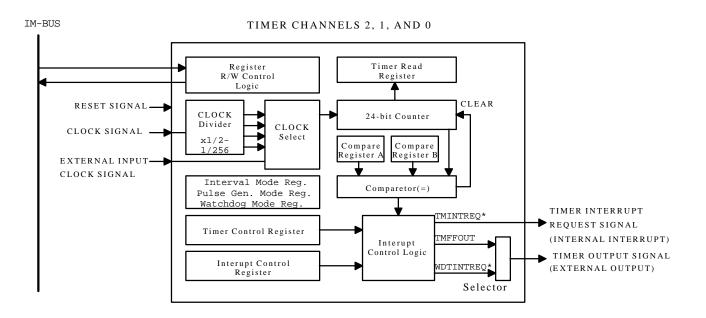

| 13 | TIME  | ERS/COUNTERS                                                                           | 196 |

|    | 13.1  | Features                                                                               | 196 |

|    | 13.2  | Block Diagrams                                                                         | 196 |

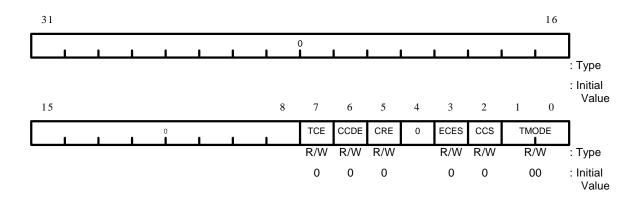

|    | 13.3  | Registers                                                                              | 198 |

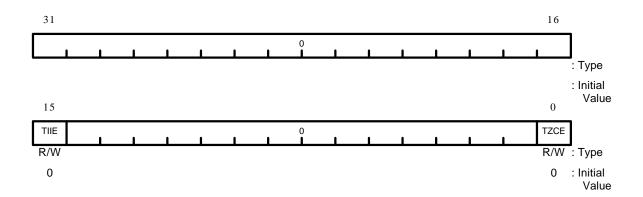

|    |       | 13.3.1 Timer control registers 2, 1, and 0 (TCR2, 1, 0)                                |     |

|    |       | 13.3.2 Interval timer mode registers 0, 1, and 2 (ITMR2, 1, 0)                         | 202 |

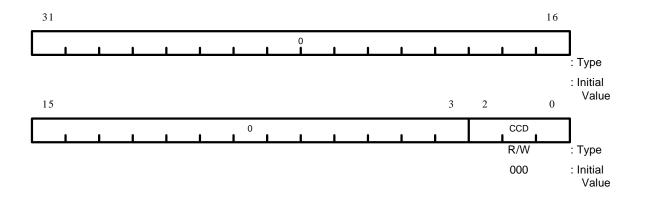

|    |       | 13.3.3 Divider registers 2, 1, and 0 (CCDR2, 1, 0)                                     | 203 |

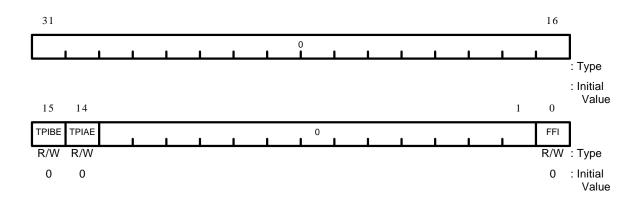

|    |       | 13.3.4 Pulse generator mode registers 2 and 1 (PGMR2, 1)                               | 204 |

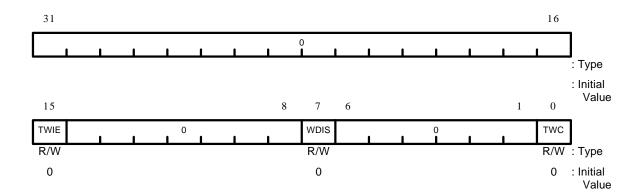

|    |       | 13.3.5 Watchdog timer mode register 2 (WTMR2)                                          | 205 |

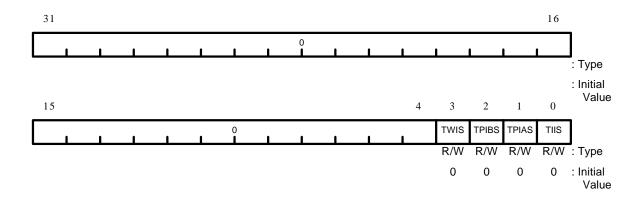

|    |       | 13.3.6 Timer interrupt status registers 2, 1 and 0 (TISR2, 1, 0)                       | 206 |

|    |       | 13.3.7 Compare registers A 2, 1 and 0 (CPRA2, 1, 0)                                    |     |

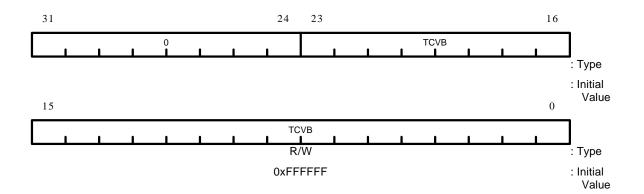

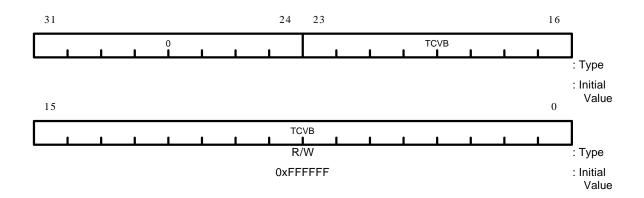

|    |       | 13.3.8 Compare registers B 2, 1 and 0 (CPRB2, 1, 0)                                    |     |

|    |       | 13.3.9 Timer read registers 2, 1 and 0 (TRR2, 1, 0)                                    | 209 |

|    | 13.4  | Operations                                                                             | 210 |

|    |       | 13.4.1 Interval timer mode                                                             | 210 |

|    |       | 13.4.2 Pulse generator mode                                                            | 213 |

|    |       | 13.4.3 Watchdog timer mode                                                             | 215 |

|    | 13.5  | Timing Explanations                                                                    | 216 |

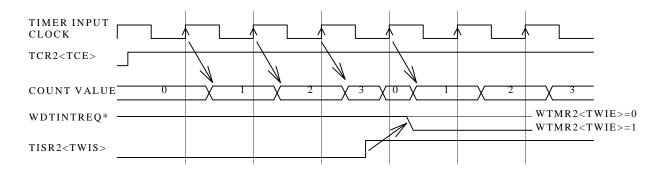

|    |       | 13.5.1 Interval timer mode interrupt timing                                            | 216 |

|    |       | 13.5.2 Pulse generator mode F/F output timing                                          | 217 |

|    |       | 13.5.3 Watchdog timer mode interrupt timing                                            | 217 |

| 14 | IO PO | DRTS (PIO)                                                                             | 218 |

|    | 14.1  | Set-Up of the Shared PIO's                                                             | 218 |

|    | 14.2  | Functions                                                                              | 218 |

|    | 14.3  | Registers                                                                              | 219 |

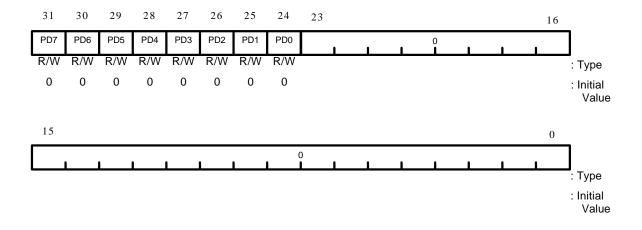

|    |       | 14.3.1 PIO data registers (PDR2, 1, 0)                                                 |     |

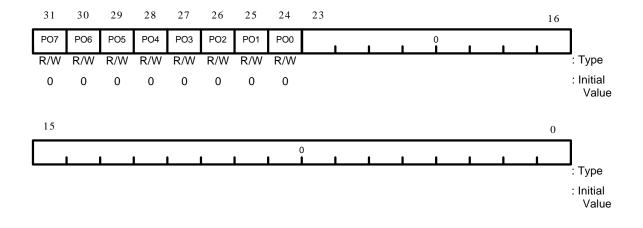

|    |       | 14.3.2 PIO direction registers (POR2, 1, 0)                                            | 221 |

# Users Manual

# 1 INTRODUCTION

# 1.1 Overview

The TMPR3904F (to be called "TX3904" hereinafter) is a standard micro controller of the 32-bit RISC Microprocessor TX39 family.

The TX3904 uses the TX39 Processor Core as the CPU. The TX39 Processor Core is a RISC CPU core Toshiba developed based on the R3000A architecture of MIPS Group, a division of Silicon Graphics, Inc. ("MIPS").

As micro-controllers that can be embedded, besides the TX39 Processor Core, the TX3904 has built-in peripheral circuits such as memory controllers, DMA controllers, serial ports, and timers/counters.

As for the architecture of the TX39 Processor Core such as the instruction set, please refer to the following document:

32-bit RISC Microprocessor, TX39 Family: Users' Manual (Toshiba Material Number: 4623-B)

R3000A is a trademark of MIPS Technologies, Inc.

# Users Manual

1.2 Notation used in this manual

# Mathematical notation

Hexadecimal numbers are expressed as follows (example shown for decimal number 42) 0x2A A K(kilo) byte is  $2^{10} = 1,024$  bytes, a M(mega) byte is  $2^{20} = 1,024 \times 1,024 = 1,048,576$  bytes, and a G(giga) byte is  $2^{30} = 1,024 \times 1,024 \times 1,024 = 1,073,741,824$  bytes.

# Data notation

Byte: eight bits Halfword: two contiguous bytes (16 bits) Word: four contiguous bytes (32 bits) Doubleword: eight contiguous bytes (64 bits)

# Signal notation

Low active signals are indicated by an asterisk (\*) at the end of the signal name (e.g.: RESET\*). Changing a signal to active level is to "assert" a signal, while changing it to a non-active level is to

"de-assert" the signal.

#### **Users Manual**

#### 1.3 Kind of accessing by the TX3904

#### Byte access

An access with a unit of eight bits. The BE\* signal shows 0111, 1011, 1101 or 1110 in 32-bit bus mode, and 1101 or 1110 in 16-bit bus mode.

#### Halfword access

An access with a unit of 16 bits. The BE\* signal shows 0011 or 1100 in 32-bit bus mode, and 1100 in 16-bit mode.

#### Triple bytes access

An access with a unit of 24 bits. The BE\* signal shows 0001 or 1000 in 32-bit bus mode. In 16-bit bus mode, one logical access is divided by two physical accesses with BE\*=1100/1101 or 1100/1110.

#### Word access

An access with a unit of 32 bits. The BE\* signal shows 0000 in 32-bit bus mode. In 16-bit bus mode, one logical access is divided by two physical accesses with BE\*=1100/1100.

### Users Manual

# 1.4 Precautions in the TMPR3904F specification

# Little endian

The TMPR3904F doesn't support little endian mode. **Don't set** a Big bit as little endian mode in the channel control register of DMAC.

### Bus error

In the TMPR3904F, if a BUSERR\* is asserted during write operation, bus control signals (BSTART\*, LAST\*, R/W\*) malfunction and a BEOW bit in a chip configuration register doesn't indicate bus error. **Don't use** this function.

### Time out error

In the TMPR3904F, if time out error occurs during write operation, an NMI is generated but a BEOW bit in a chip configuration register doesn't indicate bus error.

### Halt mode

A store instruction which sets a halt bit in the configuration register of the TX39 processor core must be placed on an address whose low four bit is 0x8. If not, the TMPR3904F may not return to the normal mode correctly. Refer to the section 6.6.2 Halt mode for more detail.

Burst mode access by the DRAMC and ROMC

The bus master issues a burst starting address for the first word, then the DRAMC/ROMC generates the successive address for the second word and after. The DRAMC/ROMC increments address like as 0-4-8-C-10-... if the lower four-bit of burst starting address is 0x0. On the other hand, it decrements address like as C-8-4-0-... if the starting address is 0xC.

### SIO external clock

In the TMPR3904F, an external clock SCLKIN can't be used for SIO boudot rate generator.

# Users Manual

SIO stop bit

In the TMPR3904F, if two-stop bit is set as a transmitter parameter, the receiver can't detect the next start bit during 1.5 bits time period after detecting a stop bit. Therefore a transmitter as a counter part of the receiver of the TMPR3904F SIO must insert an interval of 1.5 bits or more between every characters. If not, the SIO have little margin to boudot rate variance.

Bus ownership of external bus master requests

The TX39 processor core has four prioritized bus request inputs; HPSREQ, HPGREQ, SREQ, and GREQ. **Do not use** the HPGREQ and GREQ because the processor core has problem in its bus arbitration circuit. In the TMPR3904F, a bus request from an external bus master is designated by the POBus bit in the chip configuration register. A bus request of on-chip DMAC is designated by the Sreq bit in the channel control register.

2 FEATURES

■ Built-in TX39 Processor Core Toshiba has uniquely developed this on the basis of the R3000A architecture of the MIPS. Instruction cache 4KB/Data cache 1KB Built-in debug support unit ■ DRAM Controller Four-bank x two-channel configuration Fast page mode/Hyper page (EDO) mode support ■ ROM Controller Two-bank x two-channel configuration Mask ROM, EPROM, E<sup>2</sup>PROM, Flash ROM, SRAM support Page mode ROM support DMA Controller Independent four channels Single address mode/Dual address mode ■ Interrupt Controller Maskable interrupt: internal nine sources, external eight sources Non-maskable interrupt ■ Timer/Counter 24-bit up counter three channels Watchdog timer mode support ■ Serial I/0 Two-channel UART ■ I/O Ports Exclusive port: one channel; shared port: two channels ■ 16-bit Bus Support ■ Power Supply Voltage: 3.3V ■ Power Consumption: T.B.D. (3.3V, at 50 MHz operation, typ.)

- Operation Frequency: 33 50 MHz

- Package: 208 pin plastic QFP

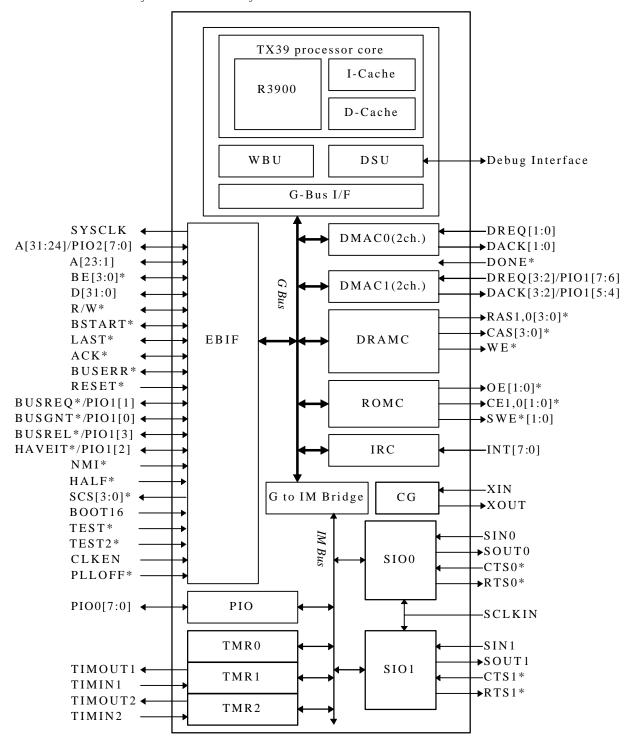

#### 3 CONFIGURATION

The following is the block diagram of the TX3904:

Fig. 3-1 TX3904 Block Diagram

#### **Users Manual**

WBU: Write Buffer

Four-store write buffer. It stores data output from the TX39 Processor Core.

DSU: Debug Support Unit

Realizes the debug function of the TX39 Processor Core.

DMAC1/DMACO: DMA Controllers

Conducts data transfers in place of the TX39 Processor Core.

DRAMC: DRAM Controller

Controls DRAM access.

ROMC: ROM Controller

Controls Mask ROM, EPROM, E<sup>2</sup>ROM, FLASH ROM, and SRAM access.

IRC: Interrupt Controller

Arbitrates interrupt requests from inside and outside the TX3904.

EBIF: External Bus Interface

Controls the bus operation of the TX3904.

CG: Clock Generator

Generates the TX3904's internal clock from external crystal oscillators.

SI01/SI00: Serial I/O's

UART.

PIO: I/O Port

8-bit port.

TMR2/TMR1/TMR0: Timers/Counters

24-bit up counters. TMR2 supports the watchdog timer function.

# Users Manual

#### 4 PINS

# 4.1 Positions of Pins

| Pin No. | Signal   | Pin No. | Signal  | Pin No. | Signal  | Pin No. | Signal  |

|---------|----------|---------|---------|---------|---------|---------|---------|

| 1       | XIN      | 31      | TOUT[3] | 61      | VDD     | 91      | DACK[0] |

| 2       | VDD      | 32      | WE*     | 62      | A[22]   | 92      | DACK[1] |

| 3       | LAST*    | 33      | A[1]    | 63      | A[23]   | 93      | DACK[2] |

| 4       | R/W*     | 34      | VDD     | 64      | A[24]   | 94      | DACK[3] |

| 5       | BE[3]*   | 35      | A[2]    | 65      | A[25]   | 95      | DONE*   |

| 6       | BE[2]*   | 36      | A[3]    | 66      | A[26]   | 96      | VSS     |

| 7       | BE[1]*   | 37      | A[4]    | 67      | A[27]   | 97      | VDD     |

| 8       | BE[0]*   | 38      | VSS     | 68      | VSS     | 98      | DREQ[0] |

| 9       | VSS      | 39      | A[5]    | 69      | VDD     | 99      | DREQ[1] |

| 10      | VDD      | 40      | A[6]    | 70      | A[28]   | 100     | DREQ[2] |

| 11      | RASO[0]* | 41      | A[7]    | 71      | A[29]   | 101     | DREQ[3] |

| 12      | RASO[1]* | 42      | A[8]    | 72      | A[30]   | 102     | HAVEIT* |

| 13      | RASO[2]* | 43      | VDD     | 73      | A[31]   | 103     | BUSREQ* |

| 14      | VDD      | 44      | VSS     | 74      | CE0[0]* | 104     | VDD     |

| 15      | VSS      | 45      | A[9]    | 75      | CE0[1]* | 105     | SCS[3]* |

| 16      | RASO[3]* | 46      | A[10]   | 76      | CE1[0]* | 106     | SCS[2]* |

| 17      | RAS1[0]* | 47      | A[11]   | 77      | CE1[1]* | 107     | SCS[1]* |

| 18      | RAS1[1]* | 48      | A[12]   | 78      | OE1*    | 108     | SCS[0]* |

| 19      | VSS      | 49      | A[13]   | 79      | VSS     | 109     | VSS     |

| 20      | RAS1[2]* | 50      | A[14]   | 80      | VDD     | 110     | PI00[0] |

| 21      | RAS1[3]* | 51      | A[15]   | 81      | OE0*    | 111     | PI00[1] |

| 22      | CAS[0]*  | 52      | VDD     | 82      | SWE0*   | 112     | PI00[2] |

| 23      | CAS[1]*  | 53      | VSS     | 83      | SWE1*   | 113     | PI00[3] |

| 24      | VDD      | 54      | A[16]   | 84      | TST02   | 114     | VDD     |

| 25      | CAS[2]*  | 55      | A[17]   | 85      | TST01   | 115     | PI00[4] |

| 26      | CAS[3]*  | 56      | A[18]   | 86      | BOOT16  | 116     | PI00[5] |

| 27      | TOUT[0]  | 57      | A[19]   | 87      | HALF*   | 117     | PI00[6] |

| 28      | TOUT[1]  | 58      | A[20]   | 88      | TEST2*  | 118     | PI00[7] |

| 29      | VSS      | 59      | A[21]   | 89      | BUSGNT* | 119     | VSS     |

| 30      | TOUT[2]  | 60      | VSS     | 90      | BUSREL* | 120     | TIMOUT2 |

| Pin No. | Signal  | Pin No. | Signal | Pin No. | Signal | Pin No. | Signal  |

|---------|---------|---------|--------|---------|--------|---------|---------|

| 121     | TIMOUT1 | 143     | D[24]  | 165     | VDD    | 187     | PCST[2] |

| 122     | TIMIN2  | 144     | D[23]  | 166     | D[7]   | 188     | PCST[1] |

| 123     | TIMIN 1 | 145     | D[22]  | 167     | D[6]   | 189     | PCST[0] |

| 124     | SCLK    | 146     | D[21]  | 168     | D[5]   | 190     | DCLK    |

| 125     | SIN1    | 147     | VDD    | 169     | D[4]   | 191     | SDAO    |

| 126     | SINO    | 148     | VSS    | 170     | D[3]   | 192     | DBGE*   |

| 127     | CTS1*   | 149     | D[20]  | 171     | D[2]   | 193     | SDI*    |

| 128     | CTS0*   | 150     | D[19]  | 172     | VSS    | 194     | DRESET* |

| 129     | VDD     | 151     | D[18]  | 173     | VDD    | 195     | TEST*   |

| 1 30    | SOUT1   | 152     | D[17]  | 174     | D[1]   | 196     | RESET*  |

| 131     | SOUTO   | 153     | D[16]  | 175     | D[0]   | 197     | ACK*    |

| 132     | RTS1*   | 154     | D[15]  | 176     | NMI*   | 198     | BUSERR* |

| 133     | RTS0*   | 155     | D[14]  | 177     | INT[0] | 199     | BSTART* |

| 134     | D[31]   | 156     | VDD    | 178     | INT[1] | 200     | VSS     |

| 135     | D[30]   | 157     | VSS    | 179     | INT[2] | 201     | VDD     |

| 136     | D[29]   | 158     | D[13]  | 180     | VDD    | 202     | SYSCLK  |

| 137     | VDD     | 159     | D[12]  | 181     | INT[3] | 203     | PLLOFF* |

| 138     | D[28]   | 160     | D[11]  | 182     | INT[4] | 204     | CLKEN   |

| 1 3 9   | D[27]   | 161     | D[10]  | 183     | INT[5] | 205     | VDDP    |

| 140     | D[26]   | 162     | D[9]   | 184     | INT[6] | 206     | VSSP    |

| 141     | D[25]   | 163     | D[8]   | 185     | INT[7] | 207     | VSS     |

| 142     | VSS     | 164     | VSS    | 186     | VSS    | 208     | XOUT    |

#### Users Manual

### 4.2 Functions of Pins

| Name of<br>Signal | 1/0 | Function                                                                                                                                                                                                                      |  |  |  |  |  |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| System Interface  |     |                                                                                                                                                                                                                               |  |  |  |  |  |

| SYSCLK            | 0   | System Clock<br>Outputs a clock with frequency either equal to or half of that of the<br>TX39 Processor Core.                                                                                                                 |  |  |  |  |  |

| A[31:1]           | 1/0 | Address bus                                                                                                                                                                                                                   |  |  |  |  |  |

| (PI02[7:0])       | 1/0 | When the TX3904 is a bus master, it is an output, otherwise input.<br>A[31:24] pins are shared with PIO.                                                                                                                      |  |  |  |  |  |

| BE[3:0]*          | 1/0 | Byte Enable<br>Indicates valid data positions on the data bus D[31:0]. When the<br>TX3904 is a bus master, it is an output, otherwise input.<br>BE[3]* : D[31:24]<br>BE[2]* : D[23:16]<br>BE[1]* : D[15:8]<br>BE[0]* : D[7:0] |  |  |  |  |  |

| D[31:0]           | 1/0 | Data bus.<br>D[15:0] is used in 16-bit bus mode.                                                                                                                                                                              |  |  |  |  |  |

| SCS[3:0]*         | 0   | System Chip Select<br>Asserts when accessing the address range that is set by the internal<br>register.                                                                                                                       |  |  |  |  |  |

| R/W*              | 1/0 | Read/Write<br>Indicates the bus operation being executed is either read or write.<br>When the TX3904 is a bus master, it is an output, otherwise input.<br>High: Read<br>Low: Write                                           |  |  |  |  |  |

| BSTART*           | 1/0 | Bus Start<br>Asserts during the first clock of the bus operation. When the TX3904<br>is a bus master, it is an output, otherwise input.                                                                                       |  |  |  |  |  |

| LAST*             | 1/0 | Last<br>Indicates that it is the last of the bus operation. When the TX3904 is<br>a bus master, it is an output, otherwise input.                                                                                             |  |  |  |  |  |

| ACK*              | 1/0 | Acknowledge<br>External circuits inform the TX3904 that the bus operation may be<br>finished. When the TX3904 is a bus master, it is an input, otherwise<br>output.                                                           |  |  |  |  |  |

| BUSERR*        | 1/0         | Bus Error                                                              |

|----------------|-------------|------------------------------------------------------------------------|

|                |             | Informs of bus errors. When the TX3904 is a bus master, it is an       |

|                |             | input, otherwise output.                                               |

| RESET*         |             | Reset                                                                  |

|                |             | Initializes the TX3904 by setting the RESET* signal low for 12 SYSCLK  |

|                |             | or more.                                                               |

| Clock          |             |                                                                        |

| XIN            |             | Crystal Input                                                          |

|                |             | Connect a crystal oscillator.                                          |

| XOUT           | 0           | Crystal Output                                                         |

|                |             | Connect a crystal oscillator.                                          |

| PLLOFF*        | 1           | PLL OFF                                                                |

|                |             | A signal to halt the PLL oscillation of the TX3904 built—in clock      |

|                |             | generator.                                                             |

| CLKEN          |             | Clock Enable                                                           |

|                |             | A signal to halt the TX3904 internal clock.                            |

| External Bus   | Master Inte | erface                                                                 |

| BUSREQ*        |             | Bus Request                                                            |

|                |             | Changes to low when the external bus master requests for the bus       |

| (PI01[1])      | 1/0         | ownership of the TX39 Processor Core.                                  |

|                |             | A pin that is shared with the PIO.                                     |

| BUSGNT*        | 0           | Bus Grant                                                              |

|                |             | Asserted when the TX39 Processor Core informs that it is releasing the |

| (PI01[0])      | 1/0         | bus ownership in response to BUSREQ*.                                  |

|                |             | A pin that is shared with the PIO.                                     |

| HAVEIT*        |             | Have It                                                                |

|                |             | Asserted when the external or internal bus master has the bus          |

| (PI01[2])      | 1/0         | ownership.                                                             |

|                |             | A pin that is shared with the PIO.                                     |

| BUSREL*        | 0           | Bus Release                                                            |

|                |             | Asserted when TX39 processor core requests the external bus master     |

| (PI01[3])      | 1/0         | to release the bus ownership.                                          |

|                |             | A pin that is shared with the PIO.                                     |

| Interrupt Sign | als         |                                                                        |

| NMI*           |             | Non Maskable Interrupt                                                 |

|                |             | Non-maskable interrupt input.                                          |

| INT[7:0]       |             | Interrupt Request                                                      |

|                |             | External interrupt request signals. Edge triggered.                    |

| Memory Interf | Memory Interface |                                                                  |  |  |  |  |

|---------------|------------------|------------------------------------------------------------------|--|--|--|--|

| RAS0[3:0]*    | 0                | Row Address Strobe                                               |  |  |  |  |

| RAS1[3:0]*    |                  | RAS signals for the DRAM.                                        |  |  |  |  |

| CAS[3:0]*     | 0                | Column Address Strobe                                            |  |  |  |  |

|               |                  | CAS signals for the DRAM.                                        |  |  |  |  |

| WE*           | 0                | Write Enable                                                     |  |  |  |  |

|               |                  | Write enable signal for the DRAM access.                         |  |  |  |  |

| OEO*          | 0                | Output Enable                                                    |  |  |  |  |

| 0E1*          |                  | Output enable of the ROM.                                        |  |  |  |  |

| CE0[1:0]*     | 0                | Chip Enable                                                      |  |  |  |  |

| CE1[1:0]*     |                  | Chip select of the ROM.                                          |  |  |  |  |

| SWEO*         | 0                | SRAM Write Enable                                                |  |  |  |  |

| SWE1*         |                  | Write enable signals of the SRAM and the Flash ROM.              |  |  |  |  |

| DMA Interface |                  |                                                                  |  |  |  |  |

| DREQ[3:0]     |                  | DMA Request                                                      |  |  |  |  |

| (0101[7.6])   |                  | — The external I/O device requests a DMA transfer.               |  |  |  |  |

| (PI01[7:6])   | 1/0              | DREQ[3:2] are pins shared with the PIO.                          |  |  |  |  |

| DACK[3:0]     | 0                | DMA Acknowledge                                                  |  |  |  |  |

|               |                  | Acknowledge signals to DMA transfer request through the DREQ.    |  |  |  |  |

| (PI01[5:4])   | 1/0              | DACK[3:2] are pins shared with the PIO.                          |  |  |  |  |

| DONE*         | 1/0              | Done                                                             |  |  |  |  |

| DONL*         | 1/0              | Input: LOW is input to terminate data transfer.                  |  |  |  |  |

|               |                  | Output: Notification that transfer ended. It is asserted for one |  |  |  |  |

|               |                  | SYSCLK time period when DMA transfer ends.                       |  |  |  |  |

| Timer/Counter | r                |                                                                  |  |  |  |  |

| TIMOUT2       | 0                | Timer Output                                                     |  |  |  |  |

| TIMOUT1       |                  | Output signals of the timer.                                     |  |  |  |  |

| TIMIN2        |                  | Timer Input                                                      |  |  |  |  |

| TIMIN1        |                  | External signals for the timer's count.                          |  |  |  |  |

| Serial Port   | •                |                                                                  |  |  |  |  |

| SIN1          |                  | Serial Input                                                     |  |  |  |  |

| SINO          |                  | Data input signals of the serial I/O.                            |  |  |  |  |

| SOUT1         | 0                | Serial Output                                                    |  |  |  |  |

| SOUTO         |                  | Data output signals of the serial I/O.                           |  |  |  |  |

### Users Manual

|     | Serial Port Control                                                   |

|-----|-----------------------------------------------------------------------|

| 0   | Control signals of the serial $I/0$ .                                 |

|     |                                                                       |

|     | Serial Clock Input                                                    |

|     | Clock input of the serial I/O. The TMPR3904F can't use this input.    |

|     |                                                                       |

| 1/0 | I/O PortO                                                             |

|     | A signal for I/O Port0. Input/Output can be set in each bit.          |

|     |                                                                       |

| 0   | Debug                                                                 |

|     | A signal for the external real time debug system. DBGE*, SDI*, and    |

|     | DRESET* are pulled up internally.                                     |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     |                                                                       |

|     | Boot 16-bit                                                           |

|     | Fix to either high or low according to the bus width of the boot ROM. |

|     | High: 16 bits                                                         |

|     | Low: 32 bits                                                          |

|     | Half Speed Bus Mode                                                   |

|     | Designates the half speed bus mode. At low, the TX3904 becomes        |

|     | the half speed bus mode so that the frequency of the bus operation    |

|     | becomes a half of the operation frequency of the TX39 Processor       |

|     | Core. Fix to either high or low.                                      |

|     | Test                                                                  |

|     | A signal for tests. Fix to high.                                      |

| 0   | Test output                                                           |

|     | A signal for tests. Leave open.                                       |

|     |                                                                       |

|     | -<br> <br> /0<br> <br> <br> <br>                                      |

Signals followed by \* are active low.

5V tolerant signals are A[31:1], BE[3:0]\*, D[31:0], R/W\*, BSTART\*, LAST\*, ACK\*, BUSERR\*, RESET\*, PLLOFF\*, CLKEN, BUSREQ\*, BUSGNT\*, HAVEIT\*, BUSREL\*, NMI\*, INT[7:0], DREQ[3:0], DACK[3:2], DONE\*, TIMIN1, TIMIN2, SIN0, SIN1, CTS0\*, CTS1\*, SCLKIN, PI00[7:0], BOOT16, HALF\*, TEST\*, TEST2\*

#### 5 ADDRESS MAPS

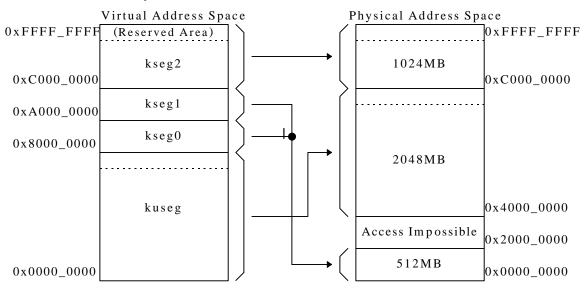

#### 5.1 Memory Map

The memory space of the TX3904 is 4 Gbytes. The memory map of the TX3904 is managed by the memory management unit (MMU) of the TX39 Processor Core. The following diagram shows the memory map of the TX3904.

As for details of the memory map of the TX39 Processor Core, please refer to: TX39 Family Users' Manual

| Segment   | Virtual Address | Physical Address | Cache      | Mode   |

|-----------|-----------------|------------------|------------|--------|

| kseg2     | 0xFFFF_FFFF     | 0xFFFF_FFFF      | Impossible | Kernel |

| (Reserved |                 |                  |            |        |

| Area)     | 0xFF00_0000     | 0xFF00_0000      |            |        |

| kseg2     | 0xFEFF_FFFF     | 0xFEFF_FFFF      | Possible   | Kernel |

|           |                 |                  |            |        |

|           | 0xC000_0000     | 0xC000_0000      |            |        |

| kseg1     | 0xBFFF_FFFF     | 0x1FFF_FFFF      | Impossible | Kernel |

|           |                 |                  |            |        |

|           | 0xA000_0000     | 0x0000_0000      |            |        |

| kseg0     | 0x9FFF_FFFF     | 0x1FFF_FFFF      | Possible   | Kernel |

|           |                 |                  |            |        |

|           | 0x8000_0000     | 0x0000_0000      |            |        |

| kuseg     | 0x7FFF_FFFF     | 0xBFFF_FFFF      | Impossible | Kernel |

| _         |                 |                  | _          | &      |

|           | 0x7F0000_000    | 0xBF00_0000      |            | User   |

|           | 0               |                  |            |        |

| kuseg     | 0x7EFF_FFFF     | 0xBEFF_FFFF      | Possible   | Kernel |

|           |                 |                  |            | &      |

|           | 0x0000_0000     | 0x4000_0000      |            | User   |

| Fig. 5-1 | TX3904 | Address Map |

|----------|--------|-------------|

|----------|--------|-------------|

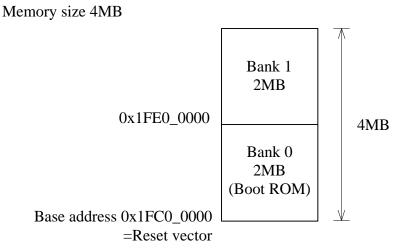

In the TX3904, the address to which memories (DRAM, ROM, etc.) are to be allocated shall be set up in the memory controller. However, Channel O of the ROM is for the boot program; so that the

#### **Users Manual**

address is determined at the time of reset.

The high-order 16 MB of kseg2 is a reserved area. The registers of the TX3904 built-in peripheral modules are assigned to this reserved area.

### 5.2 Register Map

The following is the register map of the TX3904 built-in modules:

Table 5-1 TX3904 Register Map

| Address     | Module | Register                         |

|-------------|--------|----------------------------------|

| 0xFFFF_F704 | PIO2   | Data Register                    |

| 0xFFFF_F700 | PI02   | Direction Register               |

| 0xFFFF_F604 | PI01   | Data Register                    |

| 0xFFFF_F600 | PI01   | Direction Register               |

| 0xFFFF_F504 | PI00   | Data Register                    |

| 0xFFFF_F500 | PI00   | Direction Register               |

| 0xFFFF_F430 | SI01   | Receiver FIFO Buffer             |

| 0xFFFF_F420 | SI01   | Transmitter FIFO Buffer          |

| 0xFFFF_F414 | SI01   | Baud Rate Control Register       |

| 0xFFFF_F410 | SI01   | FIFO Control Register            |

| 0xFFFF_F40C | SI01   | DMA/Interrupt Status Register    |

| 0xFFFF_F408 | SI01   | DMA/Interrupt Control Register   |

| 0xFFFF_F404 | SI01   | Line Status Register             |

| 0xFFFF_F400 | SI01   | Line Control Register            |

| 0xFFFF_F330 | SI00   | Receiver FIFO Buffer             |

| 0xFFFF_F320 | SI00   | Transmitter FIFO Buffer          |

| 0xFFFF_F314 | SI00   | Baud Rate Control Register       |

| 0xFFFF_F310 | SI00   | FIFO Control Register            |

| 0xFFFF_F30C | SI00   | DMA/Interrupt Status Register    |

| 0xFFFF_F308 | SI00   | DMA/Interrupt Control Register   |

| 0xFFFF_F304 | SI00   | Line Status Register             |

| 0xFFFF_F300 | SI00   | Line Control Register            |

| 0xFFFF_F2F0 | TMR2   | Timer Read Register              |

| 0xFFFF_F240 | TMR2   | Watchdog Timer Mode Register     |

| 0xFFFF_F230 | TMR2   | Pulse Generator Mode Register    |

| 0xFFFF_F220 | TMR2   | Event Counter Mode Register      |

| 0xFFFF_F210 | TMR2   | Interval Timer Mode Register     |

| 0xFFFF_F20C | TMR2   | Compare Register 2               |

| 0xFFFF_F208 | TMR2   | Compare Register 1               |

| 0xFFFF_F204 | TMR2   | Timer Interrupt Control Register |

| 0xFFFF_F200 | TMR2   | Timer Control Register           |

| 0xFFFF_F1F0 | TMR1   | Timer Read Register              |

| 0xFFFF_F140 | TMR1   | Watchdog Timer Mode Register     |

| 0xFFFF_F130 | TMR1 | Pulse Generator Mode Register       |

|-------------|------|-------------------------------------|

| 0xFFFF_F120 | TMR1 | Event Counter Mode Register         |

| 0xFFFF_F110 | TMR1 | Interval Timer Mode Register        |

| 0xFFFF_F10C | TMR1 | Compare Register 2                  |

| 0xFFFF_F108 | TMR1 | Compare Register 1                  |

| 0xFFFF_F104 | TMR1 | Timer Interrupt Control Register    |

| 0xFFFF_F100 | TMR1 | Timer Control Register              |

| OxFFFF_F0F0 | TMRO | Timer Read Register                 |

| 0xFFFF_F040 | TMRO | Watchdog Timer Mode Register        |

| 0xFFFF_F030 | TMRO | Pulse Generator Mode Register       |

| 0xFFFF_F020 | TMRO | Event Counter Mode Register         |

| 0xFFFF_F010 | TMRO | Interval Timer Mode Register        |

| 0xFFFF_F00C | TMRO | Compare Register 2                  |

| 0xFFFF_F008 | TMRO | Compare Register 1                  |

| 0xFFFF_F004 | TMRO | Timer Interrupt Control Register    |

| 0xFFFF_F000 | TMRO | Timer Control Register              |

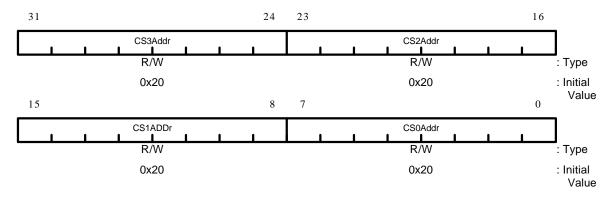

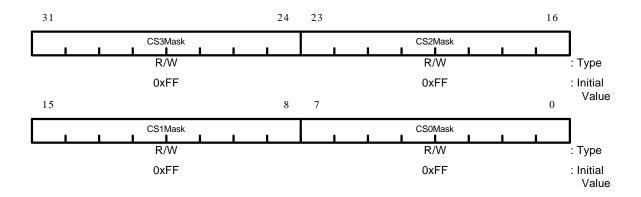

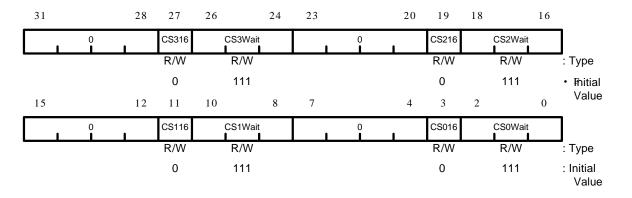

| 0xFFFF_E018 | EBIF | SCS Wait Register                   |

| 0xFFFF_E014 | EBIF | SCS Mask Register                   |

| 0xFFFF_E010 | EBIF | SCS Address Register                |

| 0xFFFF_E000 | EBIF | Chip Configuration Register         |

| 0xFFFF_C004 | IRC  | Interrupt Mask Register             |

| 0xFFFF_C01C | IRC  | Interrupt Level Register 3          |

| 0xFFFF_C018 | IRC  | Interrupt Level Register 2          |

| 0xFFFF_C014 | IRC  | Interrupt Level Register 1          |

| 0xFFFF_C010 | IRC  | Interrupt Level Register O          |

| 0xFFFF_C000 | IRC  | Interrupt Status Register           |

| 0xFFFF_B080 | DMA1 | DMA Control Register                |

| 0xFFFF_B034 | DMA1 | Next Byte Count Register (ch.3)     |

| 0xFFFF_B030 | DMA1 | Byte Count Register (ch.3)          |

| 0xFFFF_B02C | DMA1 | Destination Address Register (ch.3) |

| 0xFFFF_B028 | DMA1 | Source Address Register (ch.3)      |

| 0xFFFF_B024 | DMA1 | Channel Status Register (ch.3)      |

| 0xFFFF_B020 | DMA1 | Channel Control Register (ch.3)     |

| 0xFFFF_B014 | DMA1 | Next Byte Count Register (ch.2)     |

| 0xFFFF_B010 | DMA1 | Byte Count Register (ch.2)          |

| 0xFFFF_B00C | DMA1 | Destination Address Register (ch.2) |

| 0xFFFF_B008 | DMA1 | Source Address Register (ch.2)      |

| 0xFFFF_B004 | DMA1 | Channel Status Register (ch.2)      |

| 0xFFFF_B000 | DMA1 | Channel Control Register (ch.2)     |

| 0xFFFF_A080 | DMAO | DMA Control Register                |

| 0xFFFF_A034 | DMAO | Next Byte Count Register (ch.1)     |

| 0xFFFF_A030 | DMAO | Byte Count Register (ch.1)          |

#### **Users Manual**

|             | 1     |                                     |

|-------------|-------|-------------------------------------|

| 0xFFFF_A02C | DMAO  | Destination Address Register (ch.1) |

| 0xFFFF_A028 | DMAO  | Source Address Register (ch.1)      |

| 0xFFFF_A024 | DMAO  | Channel Status Register (ch.1)      |

| 0xFFFF_A020 | DMAO  | Channel Control Register (ch.1)     |

| 0xFFFF_A014 | DMAO  | Next Byte Count Register (ch.0)     |

| 0xFFFF_A010 | DMAO  | Byte Count Register (ch.0)          |

| 0xFFFF_A00C | DMAO  | Destination Address Register (ch.0) |

| 0xFFFF_A008 | DMAO  | Source Address Register (ch.0)      |

| 0xFFFF_A004 | DMAO  | Channel Status Register (ch.0)      |

| 0xFFFF_A000 | DMAO  | Channel Control Register (ch.0)     |

| 0xFFFF_9104 | ROMC  | Base Address Mask Register 1        |

| 0xFFFF_9100 | ROMC  | Channel Control Register 1          |

| 0xFFFF_9004 | ROMC  | Base Address Mask Register 0        |

| 0xFFFF_9000 | ROMC  | Channel Control Register 0          |

| 0xFFFF_8800 | DRAMC | Refresh Control Register            |

| 0xFFFF_8108 | DRAMC | Wait Register 1                     |

| 0xFFFF_8104 | DRAMC | Base Address Mask Register 1        |

| 0xFFFF_8100 | DRAMC | Channel Control Register 1          |

| 0xFFFF_8008 | DRAMC | Wait Register 0                     |

| 0xFFFF_8004 | DRAMC | Base Address Mask Register 0        |

| 0xFFFF_8000 | DRAMC | Channel Control Register 0          |

For details of each register, please refer to the chapter of each module. As for the SCS wait register, SCS mask register, and SCS address register of the EBIF, please refer to Chapter 7. The chip configuration register of the EBIF will be explained in the next section.

#### Users Manual

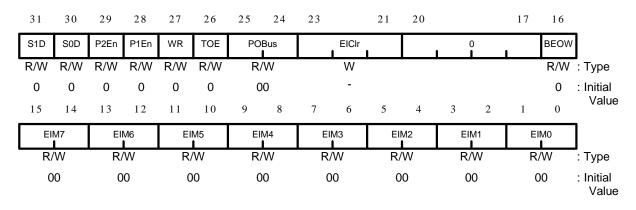

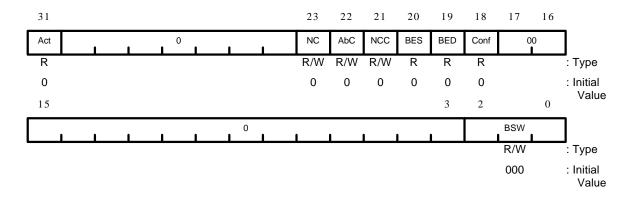

#### 5.3 Chip Configuration Register

The TX3904 has functions and pins that can be set up with software. These set-ups are conducted in the chip configuration register (CConR).

#### 5.3.1 DMA transfer of SIO

The TX3904 built-in DMA controller can, as a transfer device, select the internal SIO as well as devices outside the TX3904.

| Bit | Mnemo | Name of Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | nic   |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 31  | S1D   | SIO1 DMA<br>connection | <ul> <li>SIO1 DMA Enable (Initial value: 0)</li> <li>Selects SIO1 as the I/O device of the DMA's channel 2: i.e., the DMA transfer request signal and the DMA transfer acknowledge signal of Channel 2 will be connected to SIO1 inside the TX3904. The DREQ[2] and DACK[2] that are external pins of the TX3904 will be invalid.</li> <li>1: Channel 2 of the DMA will be connected to SIO1.</li> <li>0: Channel 2 of the DMA will be connected to the external I/O device through the DREQ[2] and DACK[2] signals.</li> </ul> |

| 30  | SOD   | SIO0 DMA<br>connection | SIOO DMA Enable (Initial value: 0)<br>Selects SIOO as the I/O device of the DMA's channel 1: i.e.,<br>the DMA transfer request signal and the DMA transfer<br>acknowledge signal of Channel 1 will be connected to SIOO<br>inside the TX3904. The DREQ[1] and DACK[1] that are<br>external pins of the TX3904 will be invalid.<br>1: Channel 1 of the DMA will be connected to SIOO.<br>0: Channel 1 of the DMA will be connected to the external I/O<br>device through the DREQ[1] and DACK[1] signals.                        |

#### **Users Manual**

### 5.3.2 PIO2 and PIO1

The TX3904 has built-in 3-channel 8-bit I/O ports (PIO2, PIO1, PIO0). Of these, PIO2 and PIO1 share their pins with others. It should be set up whether these pins are used as I/O Port pins or as other functions.

The following table shows the correspondence of the shared pins of PIO2 and PIO1:

| Bit | Mnemoni<br>c | Name of Field | Description                                                                             |

|-----|--------------|---------------|-----------------------------------------------------------------------------------------|

| 29  | P2En         | PIO2 enable   | PIO2 Enable (Initial value: 0)<br>1: Enables PIO2 for usage.<br>0: PIO2 cannot be used. |

| 28  | P1En         | PIO1 enable   | PIO1 Enable (Initial value: 0)<br>1: Enables PIO1 for usage.<br>0: PIO1 cannot be used. |

| P2En=1 | PI02[7] | PI02[6] | PI02[5] | PI02[4] | PI02[3] | PI02[2] | PI02[1] | PI02[0] |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| P2En=0 | A[31]   | A[30]   | A[29]   | A[28]   | A[27]   | A[26]   | A[25]   | A[24]   |

| P1En=1 | PI01[7] | PI01[6] | PI01[5] | PI01[4] | PI01[3] | PI01[2] | PI01[1] | PI01[0] |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| P1En=0 | DREQ[3] | DREQ[2] | DACK[3] | DACK[2] | BUSREL* | HAVEIT* | BUSREQ* | BUSGNT* |

#### Users Manual

# 5.3.3 Error processing

Sets up the watchdog interrupt from the TX3904 built-in timer/counter and bus error detection at write operation.

| Bit | Mnemo<br>nic | Name of Field                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27  | WR           | Watchdog timer<br>reset                            | Watch Dog Timer to Reset (Initial value: 0)<br>1: Connects the watchdog timer interrupt to the TX3904<br>internal reset signal.<br>0: Connects the watchdog timer interrupt to the TX3904<br>internal NMI signal.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 26  | TOE          | Time out error<br>detection                        | <ul><li>Time Out Error Enable (Initial value: 0)</li><li>1: Enable time out error detection.</li><li>0: Disable time out error detection.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16  | BEOW         | Bus error<br>occurred<br>during write<br>operation | <ul> <li>Bus Error On Write</li> <li>Indicates that a bus error was generated by a write operation of the TX39 processor core.</li> <li>Notification of anomaly is sent due to a nonmaskable interrupt if one of the following occurs: access of nonexistent register, access of nonexistent address (0xFFFF_Dxxx), or</li> <li>BUSERR* signal assert. Simultaneous to this, sets the BEOW bit to 1 and indicates that a bus error was the cause of the nonmaskable interrupt.</li> <li>1: Non-maskable interrupt was generated since a bus error occurred during a write operation of the TX39 processor core.</li> </ul> |

#### 5.3.4 Connection of external bus master

The TX3904 releases the bus ownership in response to the bus ownership request from the external master. At that time, it prioritizes the bus ownership to be given to the external bus master.

| Bit   | Mnemoni | Name of Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | С       |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25:24 | POBus   | Bus ownership<br>set-up | Priority of External Bus Request (Initial value: 00)<br>Prioritizes the bus ownership of external bus master<br>requests. The order of priority, from the highest one, is<br>HPSERQ, HPGREQ, SREG, and GREQ. At HPSREQ and SREQ,<br>the snoop function of the TX39 Processor Core works.<br>The priority of the TX3904 built-in DMAC is either SREQ or<br>GREQ.<br>11: HPSREQ (High Priority Snoop Request)<br>10: HPGREQ (High Priority General Request)<br>01: SREQ (Snoop Request)<br>01: SREQ (Snoop Request)<br>00: GREQ (General Request)<br>HPGREQ and GREQ are not able to be used. |

### 5.3.5 INT[7:0] active status clear

Clears external interrupt requests when edge mode is set up. Use the Store Byte instruction in order to write into this field. Because when the interrupt mode explained in the next section is re-written, the edge mode interrupt suspended is clear.

| Bit   | Mnemoni | Name of Field               | Description                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | С       |                             |                                                                                                                                                                                                                                                                                                                                                                   |

| 23:21 | EICIr   | External<br>interrupt clear | External Interrupt Clear<br>Clears external interrupt requests by INT[7:0]. If this field is<br>read out, the value read is 000.<br>111: Clears interrupt requests of INT[7].<br>110: Clears interrupt requests of INT[6].<br>101: Clears interrupt requests of INT[5].<br>100: Clears interrupt requests of INT[4].<br>011: Clears interrupt requests of INT[3]. |

|       |         |                             | 010: Clears interrupt requests of INT[2].<br>001: Clears interrupt requests of INT[1].<br>000: Clears interrupt requests of INT[0].                                                                                                                                                                                                                               |

#### **Users Manual**

#### 5.3.6 INT[7:0] active status set-up

Sets up the active status of the external interrupt request signal INT[7:0]. One from among the falling edge, the rising edge, the high level, and the low level of the INT[7:0] signal will be valid as an external interrupt signal. According to the setup active status, the TX3904 requests for interrupt(s) of the built-in interrupt controller. When an edge mode is set into this field, the previously suspended edge mode interrupt request is clear.

| Bit   | Mnemoni<br>c | Name of Field    | Description                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:14 | EIM7         | Interrupt mode 7 | External Interrupt Mode 7<br>Sets up the active status of the external interrupt<br>signal INT[7].<br>11: Acknowledges the rising edge as an interrupt<br>request.<br>10: Acknowledges the falling edge as an interrupt<br>request.<br>01: Acknowledges the high level as an interrupt<br>request.<br>00: Acknowledges the low level as an interrupt<br>request. |

| 13:12 | EIM6         | Interrupt mode 6 | External Interrupt Mode 6                                                                                                                                                                                                                                                                                                                                        |

| 11:10 | EIM5         | Interrupt mode 5 | External Interrupt Mode 5                                                                                                                                                                                                                                                                                                                                        |

| 9:8   | EIM4         | Interrupt mode 4 | External Interrupt Mode 4                                                                                                                                                                                                                                                                                                                                        |

| 7:6   | EIM3         | Interrupt mode 3 | External Interrupt Mode 3                                                                                                                                                                                                                                                                                                                                        |

| 5:4   | EIM2         | Interrupt mode 2 | External Interrupt Mode 2                                                                                                                                                                                                                                                                                                                                        |

| 3:2   | EIM1         | Interrupt mode 1 | External Interrupt Mode 1                                                                                                                                                                                                                                                                                                                                        |

| 1:0   | EIMO         | Interrupt mode 0 | External Interrupt Mode 0                                                                                                                                                                                                                                                                                                                                        |

**Users Manual**

#### 6 CLOCKS

6.1 Clock Generator

The TX3904 has a built-in x4 frequency PLL clock generator. Please connect a crystal oscillator with a frequency of a quarter of the internal system clock (frequency of the TX39 Processor Core's input clock).

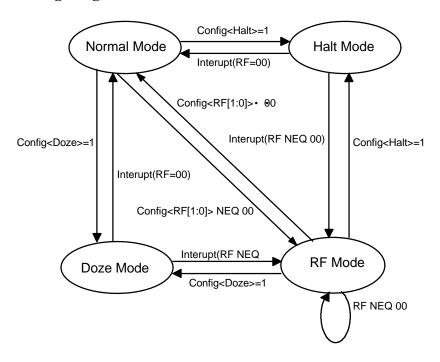

#### 6.2 Operation Modes of TX3904

The following describes the operation modes by the TX3904 clock control. The TX3904 has the normal, doze, halt, and RF modes.

6.2.1 Normal mode

Both the TX39 Processor Core and the peripheral mega cells operate at the maximum frequencies.

Blocks that operate at the same frequency as the TX39 Processor Core: DRAMC, ROMC, DMAC, IRC

Blocks that operate at the frequency that is a half of the TX39  $\ensuremath{\mathsf{Processor}}$

Core:

TMR, SIO, PIO

6.2.2 Halt mode

The halt mode is a mode to lower the power consumption by halting operations by halting the clocks inside the TX39 Processor Core. By setting the halt bit of the Config register of the TX39 Processor Core, it shifts to the halt mode.

When having entered into the halt mode, the TX39 mega cell core halts the operation while maintaining the pipeline status. Bus release requests from GREQ\* and HPGREQ\* can be replied to; but those from the SREQ\* and HPSREQ\* are not replied to. The write buffer does not halt: Therefore, when there are remaining data in the write buffer in the halt mode, the write operation continues until the buffer becomes empty. The SYSCLK does not halt.

The halt mode is released when the halt bit is cleared to 0 by asserting the interrupts by on-chip peripherals (internal interrupt), INT[7:0], NMI\*, or RESET\* signal. When the TX3904 is recovered from halt mode by the above causes, the corresponding exception handler is executed. The peripheral blocks halt partial functions by halting the clocks.

#### Halt mode is not usable in half speed bus mode.

#### **Users Manual**

The halt bit must be set to 1 with an example flow shown below in order to make the TX3904 halt mode. An exception must be caused when the TX3904 is recovered form halt mode. An interrupt must not be masked.

| address           | instruction         | comment                 |  |  |  |

|-------------------|---------------------|-------------------------|--|--|--|

| 0x????_????       | mfc0 r25, r3        | # read Config register  |  |  |  |

| 0x????_???c       | sync                | #                       |  |  |  |

| 0x????_???0       | ori r25, r25, 0x100 | # set HALT bit          |  |  |  |

| 0x????_???4       | j label             | #                       |  |  |  |

| 0x????_???8       | mtc0 r25, r3        | # write Config register |  |  |  |

| 0x????_??c label: |                     |                         |  |  |  |

A store instruction which sets a halt bit in the configuration register of the TX39 processor core must be placed on an address whose low four bit is 0x8. If not, the TMPR3904F may not return to the normal mode correctly.

#### 6.2.3 Doze mode

The doze mode is a mode to lower power consumption by partially halting the TX39 Processor Core's operations. The difference from the halt mode is that bus release requests from outside can be accepted because the doze mode halts some of the clocks inside the Processor Core. The peripheral blocks continue normal operations.

By setting the doze bit of the Config register of the TX39 Processor Core, it shifts to the doze mode.

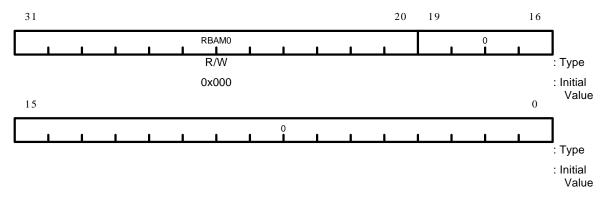

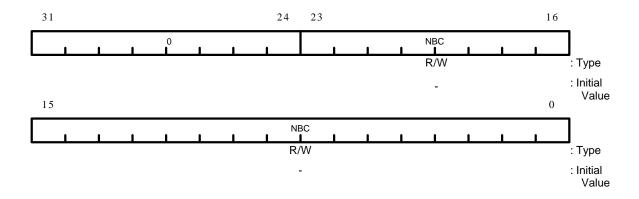

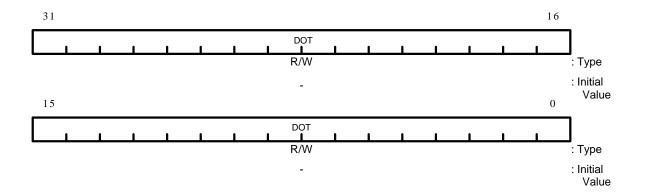

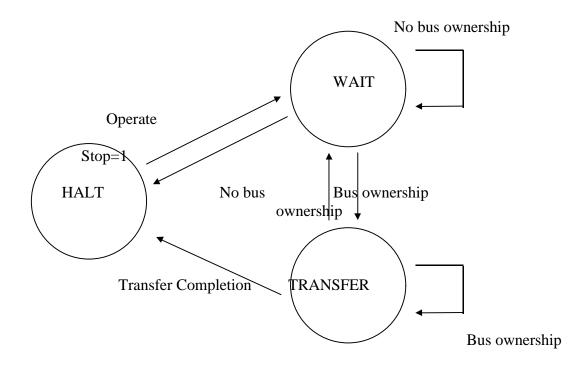

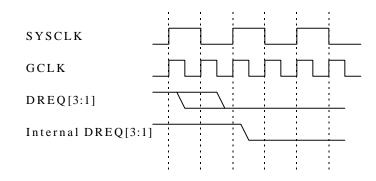

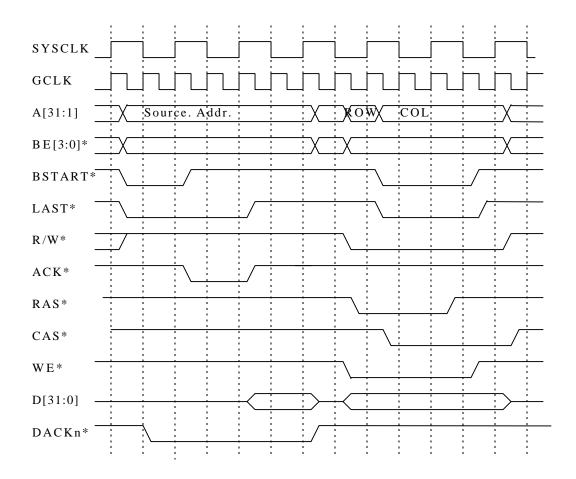

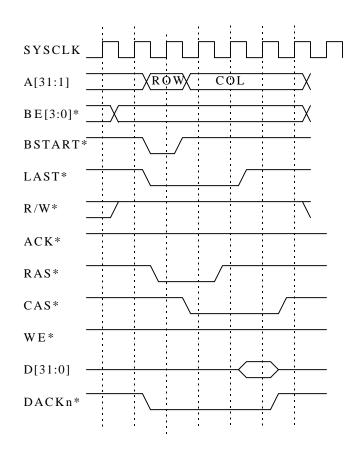

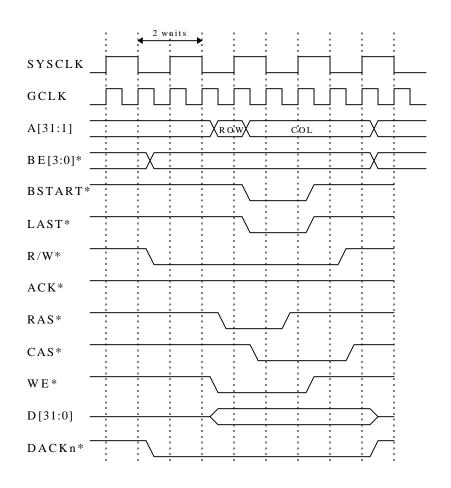

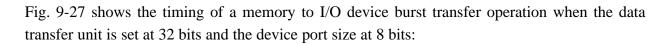

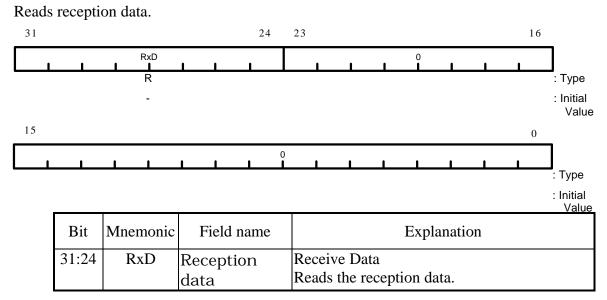

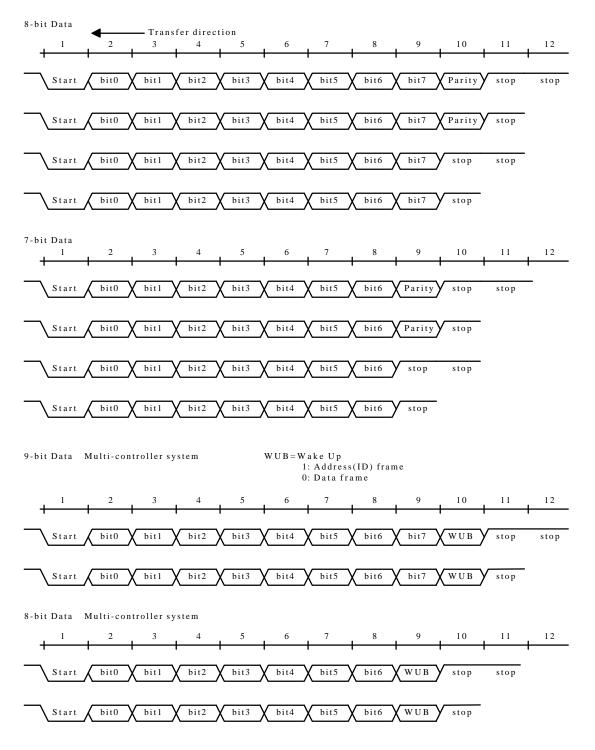

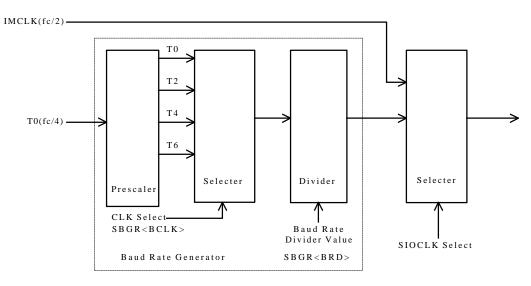

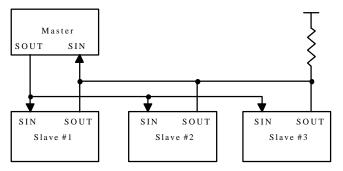

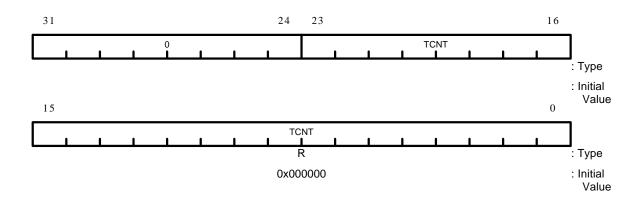

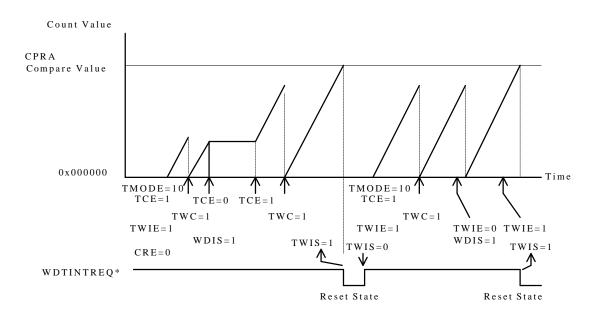

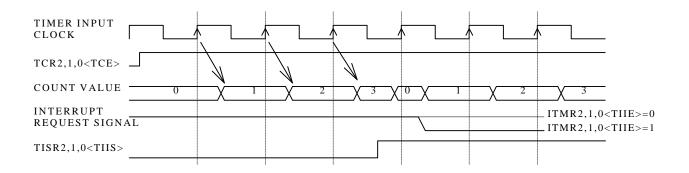

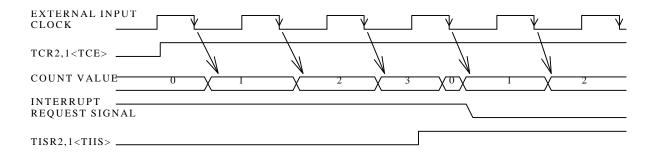

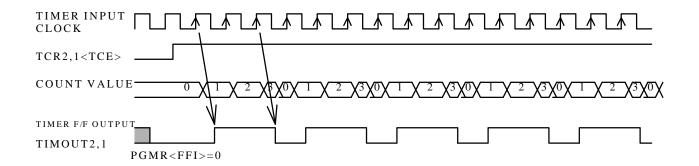

When having entered into the doze mode, the TX39 mega cell core halts operations while maintaining the pipeline status. The write buffer does not halt. Therefore, if there are remaining data in the write buffer in the doze mode, the write operation continues until the buffer becomes empty. The SYSCLK does not halt, either.