# **BONITO - PCI/SDRAM System Controller for Vr43xx**

© 1998/1999 Algorithmics Ltd Rev 2.7 of 1999/08/24

- Direct connection to any 32-bit MIPS R4x00 CPU.

- Direct connection to 32-bit 33MHz PCI bus, conforming to Rev2.1. PCI arbiter and other "host" functions available, but can also operate as a peripheral. Includes PCI mailbox registers for intelligent peripheral communication.

- Independent CPU and PCI input clocks.

- High-performance SDRAM memory system using standard PC-100 parts in either a 32- or 64-bit array, including standard 100-, 144- and 168-pin DIMMs. Glueless for small systems, but by adding synchronous buffers it allows large systems which are only one clock period slower.

- Local ROM, I/O bus connects "dumb" components, isolated from high-speed signals. DMA support for faster devices on the local I/O bus, including "UDMA" transfers as defined in the ATA-4 standard for PC disk drives.

- Internal "cache" of local memory locations provides greatly enhanced PCI transfer performance for device controllers which are PCI bus initiators.

- PCI/local-memory copier for applications requiring bulk data transport.

- Configurable debug mode makes all cycles visible at a DIMM socket.

- Glueless support of CPU reset sequence.

- Includes useful generic interrupt controller.

- Can be configured from ROM, pins or PCI bus.

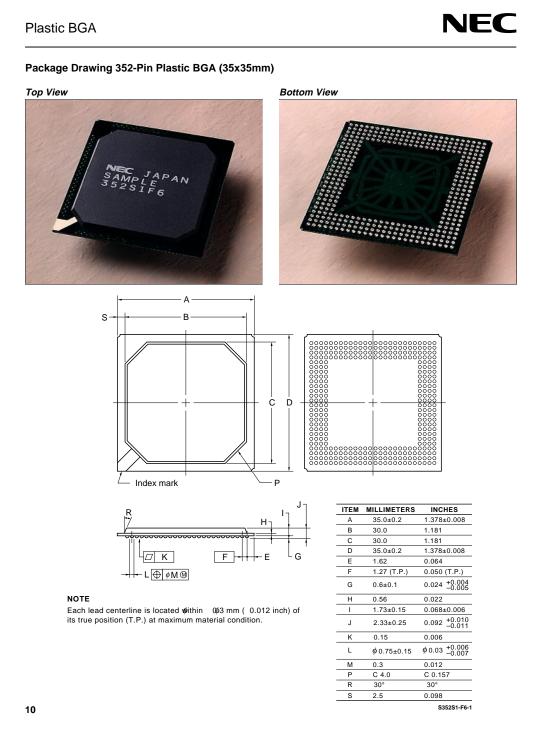

- Compact 352-pin 1.27mm pitch BGA package for reliable assembly.

- Bueno, bonito y barato!

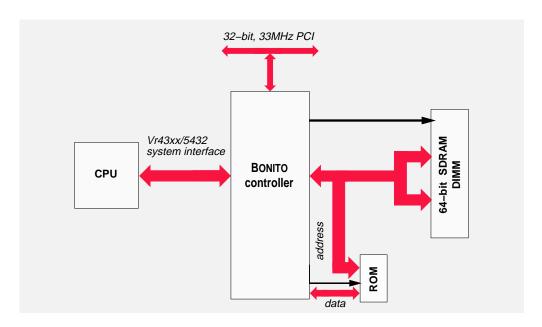

Figure 0.1 BONITO in a minimal system

# 1. Overview

This device has four ports: CPU, PCI, SDRAM and local ROM & I/O. Some SDRAM signals are used during some local ROM & I/O cycles, to provide more addresses. A minimal system block diagram is shown in Figure 0.1.

The CPU-side and PCI clocks are independent inputs, and need have no timing relationship. The SDRAM system is operated synchronously to the CPU-side clock, and should be fed, with the CPU itself, with matched low-skew clock inputs.

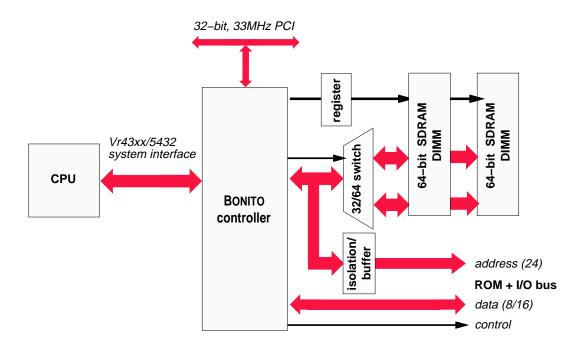

BONITO can also be used in a larger system with external buffers to allow the connection of bigger local memory arrays and more local I/O devices, as shown in Figure 1.1.

Figure 1.1 Buffered memory and expanded local I/O system

BONITO handles tasks which are common to many of those systems where a 32-bit MIPS CPU is used with a PCI bus and a local memory system. Such systems always (or almost always) need logic for some other functions, which are therefore also supported by BONITO:

- Managing the CPU reset sequence and supporting common configuration options.

- System bootstrap from local ROM or flash memory.

- High-speed transfer of data between local and PCI memory the PCI copier, described in §3.2.

- A flexible and high-performance interrupt controller, see §5.14.

- Minimal DMA support for local bus devices, see §2.4.1.

- A few general-purpose I/O pins required, for example, for access to the signature EEROM of a memory DIMM.

Within the confines of such a chip it does not make much sense to devote pins to specific I/O functions, since (unlike the above) these vary greatly from application to application.

Compared to earlier MIPS system controllers, BONITO offers a simple, fast, memory controller for PC-100 SDRAMs, with few options, and a high level of integration to minimise glue logic.

# 2. Interfaces

One way to introduce this multi-faceted part is to go around its interfaces and describe each in turn. So we'll do that for the CPU, PCI, SDRAM, ROM and I/O, GPIO, test and debug interfaces.

### 2.1. CPU Port

BONITO connects directly to any Vr43xx or Vr5432 CPU<sup>1</sup>, and variants are flexible enough to handle any 32-bit descendant of the R4000 "SysAD" bus. It will run with CPUs to 83MHz. For CPUs which support it, parity is passed through to the local SDRAM system, and generated/checked on other cycles.

BONITO manages the CPU's reset sequence. A complete reset of BONITO from its *SysReset\** pin - or the PCI *RESET\** signal where BONITO is configured as a peripheral - causes the CPU to be driven through a cold-reset sequence. BONITO supports most MIPS CPU reset models, and can supply the "mode bits" for CPU configuration when required. It's also possible to do a cold-reset of the MIPS CPU by writing a register bit; this can be used as a self-reset by CPUs which need to put themselves in a non-standard configuration: see §4.3.1 for more information.

In some cases a system may be managed by a host across PCI; it's possible to configure BONITO to wait with the local CPU stalled while an external PCI host configures the chip and uploads software to local memory; see §4.3.2.

BONITO has an internal interrupt controller, and connects to two of the MIPS CPU interrupt inputs.

# 2.2. PCI port

BONITO conforms to the PCI specification (rev 2.1), can act as initiator or target on a PCI bus, and when required can perform all host roles - it has a PCI arbiter onboard, can source the PCI reset signal, and can initiate configuration cycles.

BONITO supports CPU accesses to PCI space. CPU partial-word read or writes to PCI space are signalled with exactly the byte enables you programmed. The byte enables (and byte lanes) used can surprise you when your CPU is "big-endian"; see §4.2. CPU burst accesses (cache refills and write-backs) are not implemented to PCI memory space; the different burst termination semantics of the buses make this a hazardous and troublesome feature.

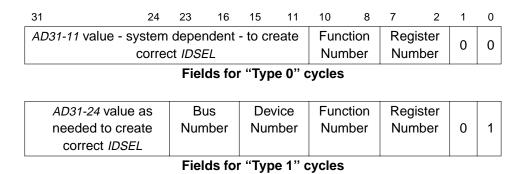

Both type 1 and type 2 configuration cycles are available through a pair of registers (one sets up the PCI address bits, and the other is a data register for configuration cycles).

CPU writes to PCI are "posted"; there's a BONITO register pcimstat which software can read to check when all posted writes have been completed on PCI.

BONITO's PCI arbiter handles up to six external initiators and operates in round-robin only. A configuration-time option allows the arbiter to be disabled, for systems whose arbiter is elsewhere; in this mode two of the arbiter signals are reconfigured to become BONITO's own request/grant lines.

BONITO makes some or all of the memory attached to its memory port available to external PCI bus masters. PCI initiator/local memory transfers go through the "I/O buffer cache", described in §3.1 below, to maintain high throughput with minimal impact on the CPU's access to local memory.

BONITO provides the standard configuration registers required by the PCI standard. Software running on the local MIPS CPU can modify some of these register contents, so that BONITO can take on different roles as part of an intelligent PCI controller; see §4.3.3.

<sup>&</sup>lt;sup>1</sup> The choice of CPU interface type is reconfigurable at reset time between Vr4300-compatible and Vr5432-native-compatible.

BONITO can be configured to respond as a PCI target to four memory address regions. One is for the BONITO's own PCI-accessible registers, and two are used for access to attached local SDRAM or I/O devices - the size, location and transfer characteristics of these two windows are influenced by some other registers. PCI access to the local I/O bus is expected to be used only for diagnostics and system initialisation; no guarantees are made about performance.

BONITO implements mailbox registers. A PCI write to a mailbox register generates an interrupt condition for the CPU, which can retrieve the data through a locally-readable register.

### 2.3. SDRAM connection

The memory interface is optimised to run burst-mode SDRAM cycles in sub-block order using PC-100 compliant memory devices. It runs in synchronisation with the CPU interface to minimise CPU access time. For small SDRAM systems - with a fan-out of 6 loads or less on all SDRAM control outputs - it is glueless. Larger systems require high-drive registered buffers (ALVCH374 or similar) for the multiplexed address lines and control signals which go to every DRAM device. When the registered buffers are used, a configuration register must be set to delay all data timings by one clock.

For pin-count reasons, the SDRAM data bus is used to carry addresses for I/O accesses requiring more than a small number of addresses - particularly for ROM cycles. I/O cycles using the SDRAM data bus cannot be run concurrently with an SDRAM access.

There's no support for SDRAM "open pages"; the cache refill and write-back traffic from the CPU has little locality of reference, and PCI traffic will be ferociously interleaved with CPU references. In this environment open pages cannot be expected to make a big impact on performance - but they make the SDRAM controller much more complex.

The SDRAM controller is optimised for 8-word burst cycles (a "word" here and throughout this specification is 32 bits), but also allows word-sized reads and writes. Memory systems supporting parity generally don't directly support writing only some bytes of the SDRAM array, so BONITO implements partial-word writes with a read-merge-write sequence.

The SDRAM control signals are designed to attach to either a 32/36-bit or 64/72-bit array. Parity generation and checking are supported on 36-bit arrays, and are a diagnostics-only option on 72-bit modules.

A single 64/72-bit SDRAM DIMM may be attached by commoning up the halves of the data bus, controlling accesses using two data-mask *DQMBHi/DQMBLo* signals - for the high and low bank respectively. But where the number of connections to the data bus grows too large, a control signal is provided for a zero-delay FET switch bus multiplexer (Quality QS3390 or similar) which connects the chips SDRAM data bus to either the high or low half of each DIMM.

In either case each cache line burst uses a single bank, so the banks are not switched at burst speed.

PCI traffic has unconditional priority for SDRAM, but PCI traffic is slow enough relative to the memory system that there are always plenty of cycles left over for the CPU.

BONITO performs refresh cycles as required.

You can configure BONITO to support any SDRAM with PC-100 compatible timing, and with up to 13 row and/or column addresses. Configuration is software driven. System software can read an on-DIMM configuration EEROM using two GPIO pins, and use that to figure out how to set up the memory controller.

# 2.4. ROM and local I/O port

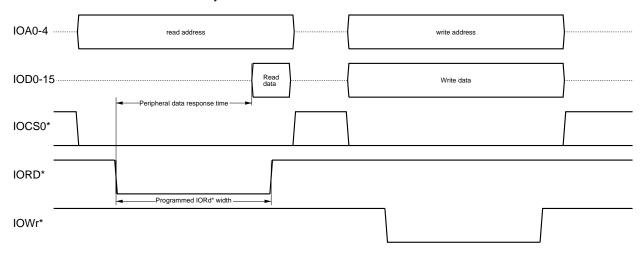

A dedicated local 16-bit I/O data bus is provided, with five dedicated I/O bus address bits. I/O bus cycles requiring more addresses find them on the SDRAM data bus. A single flash ROM device can be connected directly, but for larger systems it's desirable to isolate the I/O and ROM devices from the high-speed SDRAM cycles; so a signal *Isolate* is provided to control a bus switch or simple buffer on the address lines. It is always left disabled during SDRAM cycles.

BONITO generates Intel-style I/O device control signals, two ROM chip selects, and four I/O chip selects. ROMs must be 120ns or faster. Two fixed I/O timings are supported, corresponding to read/write pulse widths of approximately 200 and 800ns, respectively. There is no byte addressing for I/O devices; distinct I/O bus addresses are at 4-byte intervals in CPU or PCI space.

A limited I/O bus DMA facility is offered, which is particularly (but not uniquely) applicable to implementing a low-cost, high-performance IDE interface. It's described in §2.4.1.

BONITO will perform multiple reads from a ROM to service CPU word or burst reads, allowing the system to run - and to run cached - from a single 8- or 16-bit device. The assembly of ROM data into 32-bit words on the CPU bus is done in a fixed order, regardless of programmed endianness; see §4.2 for why this is probably a good idea.

### 2.4.1. "DMA" for local I/O

BONITO's local I/O bus is, quite deliberately, highly compatible with the "ISA" bus found inside all PCs. In turn that means that it is also very similar to the "IDE" disk drive interface (which started life as "ISA on a cable").

IDE peripherals are very cheap and widely available, and IDE disk drives offer very high performance where DMA is available. Recent standards like "ATA-4" have defined a series of improved DMA protocols, and BONITO implements several up to and including "Ultra-DMA" with its 33Mbytes/s burst transfer rate.

BONITO's DMA accelerator automatically cycles the local bus to read or write data in bursts of up to 32 bytes of data between a local bus DMA device and an on-chip DMA buffer. The DMA buffer can be configured to auto-flush to or auto-fill from an incrementing local memory address to provide classic DMA.

Accelerator cycles on the I/O bus are requested with a *DMARQ* input and select the port to read/write with a *DMACK\** signal.

DMA I/O bus cycles don't share any DRAM bus signals, so they can be overlapped with SDRAM accesses.

# 2.5. Interrupts and general-purpose I/O (GPIO) pins

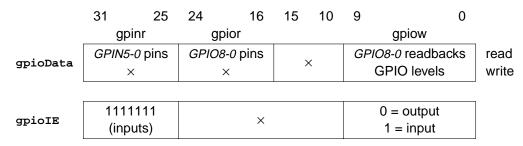

BONITO provides nine GPIO pins, programmable as input, output or tristate, and six dedicated input pins. The input pins are particularly good places to wire device interrupts, but some GPIO pins are available to the interrupt controller too, as described in 5.14.

See the signal list for hardware connections.

### 2.6. Test interfaces

The chip has a JTAG interface for boundary scan testing.

# 2.7. Debug/diagnostic facilities

When bringing up software or fault-finding in an embedded system it can be very valuable to be able to follow CPU, PCI and other transfers on a logic analyser.

BONITO is designed so that a "debug board" plugged into a DIMM socket can see the address and data of any cycle in the system. The use of the SDRAM bus for this can slow down the system, so it is controlled by a configuration register bit.

The debug board requires onboard logic - registers to capture address and data from the SDRAM pins, and logic to interpret the SDRAM-like protocol and generate address/data triggers. It's even possible to build I/O devices onto the debug board, and have them accessible in the CPU's memory map.

Electrically, the debug connector is similar to the DIMM module it supplants.

Debug signalling is described in Appendix C.

# 3. Inside BONITO

Two significant pieces of hardware are not directly related to any one of BONITO's ports, so we haven't mentioned them yet. They're:

- The I/O buffer cache, which is responsible for providing a temporary home for data in transit between local memory and an external PCI initiator.

- The PCI copier, used to transfer data between local SDRAM memory and PCI-accessible locations without (much) CPU intervention.

### 3.1. I/O buffer cache

The I/O buffer cache ("IOBC") is a small internal cache of local SDRAM locations, but it does a job you'd more often see given to a FIFO. It is used when external PCI initiators read and write BONITO's local SDRAM memory; most PCI controllers are "bus masters" and this is a critical part of many system workloads.

The IOBC translates the PCI's stream-like data accesses to the aligned cache block transfers supported by the local memory. It provides low-latency reads and writes for non-CPU transfers, and causes minimal disruption to the performance-critical CPU/memory traffic. The IOBC uses heuristics to schedule prefetches and write-backs to keep locally-sequential data flowing efficiently.

The IOBC has the following characteristics:

- The memory transfer unit is equal to the CPU's largest line size 8×32-bit words.

- The cache-line-sized data stores are organised in pairs. Data from anywhere can use any of the four pairs, but consecutive data blocks are kept together in the same pair; each contiguous data stream from a PCI master device will tend to be buffered through one pair of entries.

- The cache is small, with just four pairs of entries. But in most applications it performs well (with a low "miss rate") because PCI accesses show very strong locality of reference.

The IOBC is a write-back cache (data written from PCI into the cache is not immediately forwarded to SDRAM), but has two particular differences from a CPU cache. The first is that the cache never reads data from memory in order to service a write, as is common for CPU caches. Instead, the cache keeps track of every byte which has been written by the I/O side; when the data is written back to memory, the IOBC performs a read-merge-write operation if any of the bytes in the line have *not* been written with I/O data.

The second difference relates to how lines are chosen for replacement. When a CPU misses in its cache and a new cache location is needed for the refill data, it's normal to make some attempt to employ the "least recently used" suitable line. By contrast the IOBC keeps its lines in pairs, and tries to use just one

pair of lines for an active data stream.

When a PCI master reads or writes data from local memory through the "IO cacheable" area, the cache automatically re-allocates the pair of the line involved in a transfer to the next sequential block of memory. If the pair line was "dirty", the re-allocation causes it to be written back. If the PCI event was a read, the cache starts a memory operation to pre-fetch data into the newly allocated line.

## I/O buffer cache coherence management

Because the IOBC is a cache, we need to consider the implications for coherence between the CPU's view of local memory and that of PCI bus initiators.

The IOBC hardware "snoops" CPU/memory traffic to ensure coherency for uncached accesses from the CPU, so device drivers which use uncached memory regions to share memory with PCI masters will continue to operate.

Snooping causes clean IOBC entries to be invalidated when the CPU writes a matching memory location; dirty entries will be written back before a matching CPU read is allowed to go ahead.

IOBC coherency with respect to cached (burst) CPU transfers can be turned on, as an option. This is a useful debug/diagnostic feature - making it easy to test for device drivers which fail to handle the cache correctly. But it is not recommended for real systems; it imposes a significant penalty on every CPU burst transfer, which is a very poor performance trade-off.

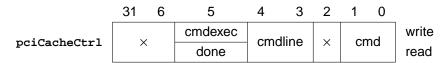

The CPU can control the state of lines in the I/O buffer cache. All I/O buffer cache lines can be written back or invalidated on CPU command. The operations might typically be invoked from within the CPU cache management functions of the board support package.

BONITO provides registers and operations which allow the CPU to inspect the state of each cache line pair, and to write-back and/or invalidate a specified line. See 5.9.1 for some programming guidelines.

# 3.2. PCI copier

Some applications require PCI memory-to-memory copy. These operations are not like conventional DMA, because they are not controlled by DMA request signals.

In an ideal world, it is good design practice to make sure that data is generated in the right place, not generated somewhere else and moved; but sometimes it can't be avoided. Such copies are problematic on the bus, because large memory-to-memory copies tend to absorb all available PCI bandwidth, increasing worst-case latency for all other bus users. BONITO provides a relatively dumb copy engine which can speed data between local SDRAM and another PCI-accessible memory.

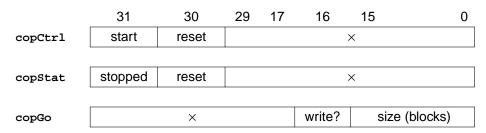

To initiate a copy the CPU writes the (word-aligned) PCI address, the cache-block-aligned local SDRAM address and a block count<sup>2</sup>. Flags determine the direction of the transfer and whether an interrupt should be raised on completion of the transfer.

Copy requests are "double-buffered", so the CPU can set up a second transfer immediately it has started the first. When the first finishes, the second will start immediately - and software can arrange to get an interrupt to warn it to set up a third transfer and so on, to keep data flowing.

Once activated the copier transfers cache-line-sized lumps of data between the PCI and local memory, until the count is exhausted. The block count is limited to 16 bits, corresponding to a 2Mbyte copy; larger transfers must be made of a chain of smaller units.

The copier only bursts to/from PCI for data which fits inside a 32-byte memory "cache block". At block boundaries it drops the PCI bus request for at least one clock to permit other PCI initiators, or other activities within BONITO, to gain the bus, thus reducing its impact on system-wide PCI transfer latency.

<sup>&</sup>lt;sup>2</sup> If the data you want to copy is not suitably aligned in local memory, you will need to copy the first few words using CPU reads/writes.

When a copy operation is completed (either its count has hit zero or there has been some non-retryable bus problem) an interrupt will be raised. When a cycle has an error the copier always raises an interrupt and stops itself.

The CPU can stop the block copier under software control (though any committed PCI access is completed first). When stopped, internal registers become accessible to the CPU: they include the current PCI address, the current local memory address, the remaining count, and a flags word describing the outcome of the last PCI cycle.

# 4. Programming BONITO

We're nearly at the point of defining registers; but there are three general issues to cover first. One is the address map, which is to some extent used by any BONITO system; the second is the confusing issue of endianness. The third brings together issues relevant to getting the system bootstrapped, at least to the point where you're running some software on the MIPS CPU.

There are hexadecimal addresses listed in the tables below, and register addresses in Appendix A; but don't re-type them! We'd like to encourage you to download a C header file from Algorithmics' internet server at ftp://ftp.algor.co.uk/pub/bonito/bonito.h; it will save you hours of typing, reduce the risk of mistakes, and means that the worldwide family of BONITO programmers will use the same register and field names. As an additional incentive, the online version is more likely to be up-to-date<sup>3</sup>.

Where you see register names in bold fixed point font, they're names used in the online header file. And when you see a register name with a "dot" in it (e.g. sdcfg.awidth64), that means we're talking about the field called awidth64 in the register sdcfg.

# 4.1. Address maps

The view of the system from the CPU is somewhat different from that as seen by a PCI bus initiator. We describe both.

### **CPU** access map

| Base<br>Address        | Size<br>(bytes) | Class     | Description                                                                                                                                                                                              |

|------------------------|-----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 0000              | 256M            | Memory    | local SDRAM memory                                                                                                                                                                                       |

| 1000 0000              | 64M             | PCI_Lo0   | PCI low-memory bus window for most CPU accesses to PCI space. Each of the                                                                                                                                |

| 1400 0000              | 64M             | PCI_Lo1   | three 64Mbyte windows can be separately positioned in PCI space with its own                                                                                                                             |

| 1800 0000              | 64M             | PCI_Lo2   | base register.                                                                                                                                                                                           |

| 1c00 0000              | 32M             |           | ROM (suitable for soldered flash) selected by ROMCS1*.                                                                                                                                                   |

| 1e00 0000              | 24M             | ROM       | unused                                                                                                                                                                                                   |

| 1f80 0000              | 4M              |           | ROM (probably a socket, to provide a first-run bootstrap) selected by ROMCS0*.                                                                                                                           |

| 1fc0 0000              | 1M              | Boot      | Bootstrap memory location - starts at the magic MIPS reset-time entry point.  According to reset-time configuration - see Table 5.2 - this can be mapped to 1M of either ROM space (ROMCS0* or ROMCS1*), |

| 1fd0 0000              | 1Mb             | PCI I/O   | PCI I/O space - window to the low megabyte of PCI address range: used (and probably <i>only</i> used) to access the I/O space of an attached "ISA" bus.                                                  |

| 1fe0 0000              | 256             | BONITO    | BONITO's own PCI configuration space registers available to other PCI bus masters                                                                                                                        |

| 1fe0 0100<br>1fe0 0200 | 256             | BONITO    | BONITO's internal registers. unused                                                                                                                                                                      |

| 1fe8 0000              | 512K            | PCI       | PCI configuration space reads/writes. Low parts of the address value driven on PCI comes from this address; high order bits from the pcimap_cfg register.                                                |

| 1ff0 0000              | 256K            |           |                                                                                                                                                                                                          |

| 1ff4 0000              | 256K            | Local I/O | Local I/O bus devices decoded by IOCS0-3* respectively                                                                                                                                                   |

| 1ff8 0000              | 256K            | Local I/O | Local 1/0 bus devices decoded by 10000-5 Tespectively                                                                                                                                                    |

| 1ffc 0000              | 256K            |           |                                                                                                                                                                                                          |

| 2000 0000              | 1.5Gb           | PCI_1.5   | Maps 1-1 onto PCI addresses. Most likely not very useful.                                                                                                                                                |

<sup>&</sup>lt;sup>3</sup> The great advantage of bonito.h is that we use it to build our software. But the file might have obsolete or unused definitions in; we'll try to zap them, but if the file describes something which isn't in the manual, it quite likely isn't in the chip either.

| Base<br>Address | Size<br>(bytes) | Class | Description                                                                                                                                                                                                                |

|-----------------|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8000 0000       | 2Gb             | PCI_2 | PCI access window. Optionally mapped with either 1-for-1 addresses, or mapped down to the low 2Gb of PCI space. Available if you need access to a larger region of PCI space than is available in the lower-memory window. |

|                 |                 |       | You'll need to program the MIPS TLB or use 64-bit pointers to get addresses bigger than 0x2000 0000 out of the CPU.                                                                                                        |

Table 4.1: CPU/local bus address map

### Notes on CPU memory map and guidelines for PCI windows

In an ideal PCI system, all memory locations are dynamically set up by the system host controller at boot time. However, in many cases low PCI addresses cannot always be freely allocated; space below 1Mbyte or 16Mbyte may be required for certain PC "legacy" adapters and PC-world south bridge chips, which map ISA's 20- and 24-bit addresses into the lowest part of PCI space.

In a system which might want to use such legacy devices auto-configured PCI devices should be allocated addresses from at least 1Mbyte and perhaps 16Mbytes up.

### From-PCI map

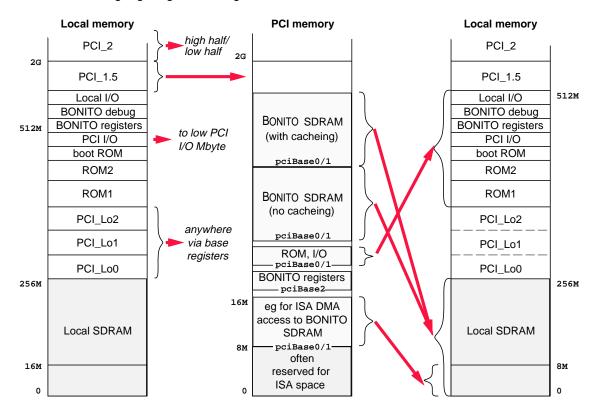

You can see how it might go together in Figure 4.1.

Figure 4.1 Memory regions and mappings between local and PCI space

The PCI regions identified (working from the bottom up):

Reserved for ISA registers/memory: if your system uses an ISA bus, or (perhaps more cogent) any

controller which needs to offer a programming model compatible with some old PC hardware, then it

may need to use registers or memory locations in the low 16Mbytes, and guite likely the low 1Mbyte.

- of PCI space. It's therefore often wise to avoid using this region for anything else.

- For ISA DMA access to BONITO SDRAM (example): more obscure. If your system may at some time support a DMA device which operates from an attached ISA bus, then that DMA device will itself only be able to reach PCI addresses in the low 16Mbytes; so it's useful to be able to map some of our SDRAM to this location. You can see here that it's possible to use one of the pciBase0-1 registers with its mask and offset defined to access only 8Mbytes of local SDRAM.

- BONITO registers: here and subsequently, the name in bold (pciBase2) is a base register determined at configuration time.

- This region provides the PCI view of BONITO's internal registers. All registers are mapped at the same position relative to the PCI base as they are mapped in CPU space.

- BONITO ROM, I/O (example): a view of the BONITO ROM and local I/O space. There's nothing to stop

you trying to go through BONITO to that part of the PCI bus mapped into local memory but it's bizarre

and not much is guaranteed.

- BONITO SDRAM (with and without IO caching) (examples): we show two large windows mapping all

the SDRAM once for accesses where IO caching is undesirable, and once for accesses where IO

caching is a good idea. You can setup BONITO to provide a PCI window to any power-of-two sized

aligned region of local memory.

If BONITO attempts a transfer which should decode as a self-access (to either BONITO registers or its attached local memory) then it will not respond on the PCI bus unless the access maps to local SDRAM (where such cycles are useful for IO buffer cache diagnostics). In all other cases the cycle will finish with a "Master Abort"<sup>4</sup>.

### 4.2. Endianness

A system has "endianness" if it supports both byte-wide and larger-integer accesses to the same memory object. A little-endian system is one where the least significant bits of the larger integer are stored in the lowest addresses, and a big-endian system is one where the most significant bits of the larger integer are found at the higher addresses. Neither is right, though each is "obvious" in different circumstances; it's a curse of computing that different CPUs and buses adopt opposite conventions. It's virtuous to write software which works with either endianness, but virtue always demands sacrifice; porting a code-base which has only ever run with one convention can be hard work.

The PCI bus is little-endian, and most PCI peripherals are little-endian in all their dealings over PCI<sup>5</sup>. A MIPS CPU may be configured to run with either endianness. Although the presence of the PCI bus is a good reason to make your CPU little-endian, sometimes an existing code base may sway the balance the other way.

So BONITO's "endianness" may be configured at reset time and changed at any time<sup>6</sup> by a software-writable 32-bit register. Endianness affects the interpretation of a MIPS CPU's uncached partial-word reads and writes, where it is necessary to steer read or write data to/from the correct byte lane of the system bus, so BONITO must agree with the CPU's configured endianness before any partial-word accesses can work.

<sup>&</sup>lt;sup>4</sup> This is only to be relied on for configuration space cycles.

<sup>&</sup>lt;sup>5</sup> Some PCI controllers do advertise facilities to help out systems with big-endian components; but everyone gets so confused about this stuff that our first recommendation is to turn all those things off and sort the problem out using software and BONITO's facilities.

<sup>&</sup>lt;sup>6</sup> In practice you'll change it (if at all) once very early in the bootstrap process.

## **Endianness and the SDRAM port**

Data is conveyed between the CPU's 32-bit data path and the SDRAM's 32-bit data path through corresponding bit numbers. No attempt is made to do anything sensible with data in SDRAM across an endianness change; the results are undefined.

## **Endianness and ROM cycles**

Local ROM data is always "little-endian" in that a byte whose address in the ROM device is 0 modulo 4 will always be presented to the CPU on *SysAD0-7*. This relationship is deliberately kept independent of configured endianness. We do that because some MIPS CPUs (notably NEC's Vr4300) can be set to either endianness purely by software.

The ROM's fixed bit-to-address mapping means that when you make sub-word accesses to ROM from a big-endian CPU the address at the ROM pins is actually flipped (at the byte-within-word level) relative to that coming out of the CPU.

Any read from ROM which can't be achieved with a single ROM cycle is (for simplicity) implemented by reading all four bytes and letting the CPU ignore the data it didn't want. Only single-byte reads from an 8-bit device or half-word reads from a 16-bit device are guaranteed to result in a single cycle at the ROM pins - something you need to know when programming most flash devices.

ROM write operations are only ever single-cycle.

### Endianness and local I/O accesses

You are recommended to connect I/O bus device's addresses to *IOA2* and upwards, so that registers appear on 4-byte-aligned locations. Access these registers with word-wide (32-bit) load and store instructions for endianness-indpendent software. Of course, only the parts of the CPU's data word which is actually connected to the device data bus are important. During I/O reads and writes the data bus *IOD0-15* feeds or is fed by the CPU data bus *SysAD0-15*.

When you do byte or other partial-word transfers from a MIPS CPU the active byte lanes depend on the CPU's endianness, so byte- or partial-word accesses to the local I/O bus can only be programmed correctly once you know the endianness of your CPU.

### Endianness and I/O bus (IDE) DMA

The IDE disk bus - and any similar 16-bit data channel - has endianness; when two bytes of data are passed along the IDE cable the byte on *IOD7-0* is earlier in sequence than the byte on *IOD15-8*. To preserve this view of byte sequence for a big-endian CPU, there's a swapper built into the IDE DMA hardware; you can enable it at iodevCfg.wordswapbit\_ide, described in Table 5.12.

### Endianness and PCI transfers, CPU and bus-initiated

When the CPU and its interface are big-endian there is bound to be trouble with accessing devices and memory over PCI bus. In this case we recommend that all CPU reads and writes of PCI locations, and PCI master accesses to local SDRAM, should be routed through BONITO's byte-lane swapper. There are two configuration bits to set, described in Table 5.3: bonGenCfg.mstrbyteswap and bonGenCfg.byteswap.

With all PCI transfers swapped, your local CPU and PCI will share a common view of byte addressing, but means that bigger-than-byte integers out in PCI world - 32-bit device registers, for example - will appear byte-swapped to the big-endian MIPS CPU; your software will need to cope.

The byte-lane swapper does not affect PCI accesses to internal BONITO registers; they're defined as 32-bit aligned objects and are generally OK. Local CPU software should avoid doing byte or other partial word transfers with BONITO registers.

## **Endianness and bootstrapping**

When the system starts up BONITO is operating with undefined endianness. Since this may not match the CPU's ideas, you can not (at this stage) rely on BONITO correctly interpreting any partial-word read or write operation from the CPU. You must program BONITO's CPU configuration register really, really early!

# 4.3. Bootstrapping

From a cold start, some MIPS CPUs require a fairly complex reset sequence; BONITO takes care of it. Most MIPS CPUs require some reset-time configuration. Where this is static, your design needs to include the appropriate pull-ups/downs; but some MIPS CPUs rely on clocking in a bit-stream from a configuration ROM. The MIPS interface - the CPU drives the clock and looks for serial data - is incompatible with low-cost serial ROMs. But here again BONITO will handle it.

In addition BONITO can perform a software-initiated reboot of the MIPS CPU, as if from a cold reset. This can be valuable in that it permits a CPU to come up in some "default" configuration, set-up BONITO's internal registers with an alternate CPU configuration and then reset itself, ending up in a software-determined configuration. See §4.3.1 below.

In most BONITO applications the MIPS CPU will bootstrap from a local ROM; you can specify either of the ROM chip select options, and choose an 8-bit or 16-bit ROM. However, it's also possible for a host attached over the PCI bus to hold the local MIPS CPU while the remote host uploads software into local SDRAM memory; described in §4.3.2.

## 4.3.1. CPU-specific reset options and "mode bits"

All the MIPS CPUs compatible with BONITO are to some extent hardware-configured to match the system they run in. Many of them retain a scheme first found in the MIPS R4000, which loads configuration bits as a serial bit-stream at reset time<sup>7</sup>. The R4000 was introduced when serial ROMs were relatively rare, and it's just bad luck that the simple interface the CPUs require is annoyingly incompatible with low-cost serial ROMs.

So BONITO provides a limited facility which - with most CPUs in most systems - will get the system up and running with an absolute minimum of additional hardware.

From a hard BONITO reset, the first 32 bits of the data stream are obtained by inverting the levels on the (weakly pulled-up on chip) CPU data bus *SysAD0-31*, starting with bit 0. Since the CPU will not be driving the bus at this point an external pull-down on any *SysAD* signal puts a "1" in the corresponding position in the mode bits stream. Most CPUs can be at least brought into a minimal working mode with a configuration with very few "1" bits.

If this allows you to get exactly the configuration you want, that's fine; but if you need something more subtle the CPU can now move on to reset itself using the bongencfg.cpuselfreset register bit. A CPU self-reset does not reset BONITO and in this case the mode bit stream is fed from the register intpol, which is borrowed for this purpose. So long as the SysAD-defined settings are enough to run a simple piece of ROM software, the software can store the configuration of its choice into intPol and reconfigure the CPU accordingly.

<sup>&</sup>lt;sup>7</sup> NEC's Vr43x0 and Vr5432 CPUs don't do this; they use only static configuration augmented by internal software-writable registers.

## 4.3.2. Choice of boot memories and PCI-initiated bootstrap

BONITO can be configured to allow its attached CPU to bootstrap from either of the two ROM regions provided in its standard address map (selected by *ROMCS0\** or *ROMCS1\**).

The two ROM regions are not equivalent; the *ROMCS0\** window is much smaller (4Mbytes maximum) and is intended for a first-time-only bootstrap for designs which have flash memory soldered using *ROMCS1\**, and need some way to get that flash device programmed in production.

However, it's possible to build a BONITO system with no ROM, where the MIPS CPU bootstraps from local DRAM memory. Booting from DRAM is only useful, of course, after someone has put a program into it; and this could only have been done by a PCI bus master which has taken control of the system.

The sequence for a PCI bootstrap is fairly complex, and the details are beyond the scope of this manual<sup>8</sup>. But the basic sequence goes like this:

- 1. BONITO should be reset but configured to preset the bonPonCfg.romBoot field to the magic "11" value you'll need pull-ups on a couple of *IOD* lines to get this effect.

- With this setting, the MIPS CPU will be held in reset after BONITO comes up.

- The PCI-located host can now program BONITO from the PCI side remember, all BONITO registers can be reached from PCI. The PCI host must initialise much of BONITO - in particular its SDRAM controller.

- 3. The PCI-located host can now fill SDRAM memory with a bootstrap program.

- 4. The PCI host re-writes bonPonCfg.romBoot to the value "10". This will cause the MIPS CPU to be taken through its normal reset sequence, but its normal start-up address will now map to local SDRAM. From now on the MIPS CPU can take control.

## 4.3.3. Software-determined PCI configuration characters

The PCI specification lays down a standard "configuration space" and standard register format in every controller, as part of a larger scheme in support of automatic configuration of a large range of possible systems - what PC software suppliers have called "plug and play". When a PCI system is reset one CPU (the "PCI host") scans the bus reading configuration space, allocating memory space and enabling drivers as required.

BONITO can be used in two roles. If the MIPS CPU is the PCI bus host, then BONITO's configuration space facilities are not very important - only the host *writes* PCI configuration space, and most of the time only the host reads it. But BONITO can also be used to build a subsystem - an intelligent controller. If, for example, you build a RAID disk controller you would like the host reading BONITO configuration registers to see a disk controller, not a "MIPS CPU bridge".

Three facilities in BONITO are available to help with this:

- 1. BONITO's configuration-space registers even those which the PCI specification assumes are only ever read by the host may in fact be overwritten by the MIPS host, thus changing its identity.

- 2. PCI configuration-space base registers are read by the host to establish the size of the memory regions a PCI device will share with the bus, and written by the host to establish their location within the overall PCI memory map.

BONITO's windows onto its internal memory may be very large; large windows are essential for some applications. But fixed-size large windows provide problems for the configuring host, which may run out of PCI memory space to allocate.

<sup>&</sup>lt;sup>8</sup> Some BONITO-related software is available free from Algorithmics; see http://www.algor.co.uk, ftp://ftp.algor.co.uk/pub/bonito/ or mail us at bonito@algor.co.uk

- So the apparent size of the regions mapped by BONITO's base registers can be changed by the MIPS CPU.

- 3. All this would be useless if the host were to complete its PCI bus initialisation before the local CPU had got around to setting up new values in BONITO's configuration-space registers. So there's also an BONITO option available as a reset-time configuration bit bonPonCfg.configdis- which causes BONITO to defer host processing, by responding with a PCI "retry" to any configuration-space access. Local software should hurry to fix up BONITO's configuration space registers before the host software times out.

# 5. Software-accessible Registers and programming

We'll organise this programming guide starting at reset time and working forwards through the operations of the chip.

BONITO's functions are controlled through a collection of registers. Apart from a few whose organisation is dictated by the PCI specification the registers are all 32-bits in size, even where only some of those bits have any meaning. They should always be read and written as whole 32-bit words.

All BONITO internal registers are accessible to both the CPU and an external PCI master. Moreover, within the relevant memory region, the register offsets are the same as seen from both sides. Of course, the fact that it's possible to access registers from both sides doesn't commit us to solving problems caused by simultaneous access - you can, but often you shouldn't!

# 5.1. Register Summary

| Register     | Page/figure   | What is it                                                              |  |  |

|--------------|---------------|-------------------------------------------------------------------------|--|--|

| bonGenCfg    | 19/Table 5.3  | Early boot-time configuration, mostly PCI-related                       |  |  |

| bonPonCfg    | 18/Table 5.2  | Configuration bits which can be set either way using <i>IOD</i> pullups |  |  |

| copCtrl      | 30/Figure 5.5 |                                                                         |  |  |

| copDAddr     | 30            |                                                                         |  |  |

| copGo        | 30/Figure 5.5 | PCI copier registers                                                    |  |  |

| copPAddr     | 30            |                                                                         |  |  |

| copStat      | 30/Figure 5.5 |                                                                         |  |  |

| gpioData     | 36/Figure 5.8 | GPIO level read/write                                                   |  |  |

| gpioIE       | 36/Figure 5.8 | GPIO input/output setting                                               |  |  |

| intEdge      | 36/Table 5.13 | Interrupts selected as level/edge triggered                             |  |  |

| intEn        | 37/5.14       | Separate interrupt enable bits                                          |  |  |

| intEnClr     | 37/5.14       | Interrupt enables - per-bit clear                                       |  |  |

| intEnSet     | 37/5.14       | Interrupt enables - per-bit set                                         |  |  |

| intISR       | 37/5.14       | Readable interrupt inputs                                               |  |  |

| intPol       | 37/5.14       | Interrupt polarity                                                      |  |  |

| intSteer     | 37/5.14       | Which of two CPU interrupt pins gets raised by each interrupt condition |  |  |

| iodevCfg     | 34/Table 5.12 | I/O bus cycle characteristics                                           |  |  |

| ldmaAddr     | 35            |                                                                         |  |  |

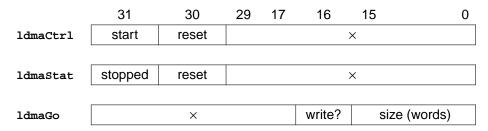

| ldmaCtrl     | 35/Figure 5.7 | I/O hara DMA are eastly for IDE                                         |  |  |

| ldmaGo       | 35/Figure 5.7 | I/O bus DMA, mostly for IDE                                             |  |  |

| ldmaStat     | 35/Figure 5.7 |                                                                         |  |  |

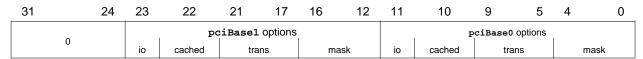

| pciBase0     | 24/Table 5.5  | Base registers in PCI configuration space,                              |  |  |

| pciBasel     | 24/Table 5.5  | which define what regions BONITO makes                                  |  |  |

| pciBase2     | 24/Table 5.5  | available to other PCI initiators.                                      |  |  |

| pciCacheCtrl | 32/Table 5.10 | Registers for the I/O buffer cache (also                                |  |  |

| pciCacheTag  | 32/Table 5.11 | known as "PCI cache").                                                  |  |  |

| Register      | Page/figure   | What is it                                                                                                   |  |  |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------|--|--|

| pciClass      | 24/Table 5.5  |                                                                                                              |  |  |

| pciCmd        | 26/Table 5.7  |                                                                                                              |  |  |

| pciDid        | 24/Table 5.5  | Standard PCI configuration registers                                                                         |  |  |

| pciExpRBase   | 24/Table 5.5  | Standard FCI configuration registers                                                                         |  |  |

| pciInt        | 24/Table 5.5  |                                                                                                              |  |  |

| pciLTimer     | 24/Table 5.5  |                                                                                                              |  |  |

| pciMail0-3    | 36/5.12       | Mailbox registers                                                                                            |  |  |

| pcimap        | 28/Table 5.9  | Register to fix the windows available to the local CPU to access PCI memory or devices.                      |  |  |

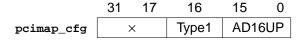

| pcimap_cfg    | 29/Figure 5.4 | Used to complete the PCI address when the local CPU is using BONITO to perform PCI configuration cycles.     |  |  |

| pcimembaseCfg | 25/Figure 5.1 | Used by local host to size and position the PCI-accessible windows into BONITO's local memory and local I/O. |  |  |

| pciMStat      | 29/Table 5.10 | How many posted writes are still pending?                                                                    |  |  |

| sdCfg         | 21/Table 5.4  | Set up BONITO to match the SDRAM shape, size, speed etc                                                      |  |  |

Table 5.1: All registers

# 5.2. General principles for BONITO registers (read this)

Don't type in these register or field names; as we already said at the start of §4 above, go to Algorithmics' ftp site and download ftp://ftp.algor.co.uk/pub/bonito/bonito.h.

To avoid lengthening the whole manual with endless repetition, the following general rules apply to the use of BONITO's registers:

- All registers are writable unless explicitly stated to be read-only.

- Wherever it is reasonable to do so and unless the detailed description says otherwise you can read back the value you last wrote to a BONITO register.

- Some options affect BONITO's support for the CPU bootstrapping itself, so must be settable at reset time. Register fields representing these options take their values by sampling the signals *IOD0-15* (the IO data bus) while the system reset *SYSRESET\** is still active. BONITO has a weak internal pull-down on each *IOD* signal line, so to set one of these register fields to 1 your system should have an external pull-up resistor on the corresponding line; a 4.7KΩ resistor to 3.3V is recommended.

- These configurable bits are gathered together into the bonPonCfg register.

- Even earlier in reset, some MIPS CPUs use a serial data stream ("mode bits") to load configuration information; see §4.3.1 for where those bits come from.

- Many other register bit-fields are forced to a fixed level (most often zero, occasionally 1) following

reset. However, this manual will document that only when it's important to early operation. Your

software should take responsibility for programming all relevant registers to reasonable values early in

the bootstrap sequence.

- Register bit fields which are not defined in this manual are just that undefined; they will be marked with a "x" in the tables. They'll most often read zero, but that's not guaranteed; and they should always be written zero. Absolutely anything might happen if you write them to something other than

We make only one promise about these values. In read/write registers it will always be safe to write an undefined field with the data you just read from it.

# 5.3. Configuration register

The bonPonCfg register brings together BONITO control bits which may be set to either 1/0 at reset time. To get a 1 value following reset in a bonPonCfg field, you need a pull-up on the corresponding IOD0-15 signal; to get a zero, make sure that all devices connected to the line are tri-state during reset (they normally will be). In fact, bonPonCfg is really 18 bits long, and the two highest bits show the reset-time value of ROMCS0-1\*; like other bits in the register which have no hardware effect, they could be used for software configuration information. Here are the fields which have a hardware effect:

#### bonPonCfg register

| Bit(s) | Name        | Value / Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14     | CPUbigend   | 1 to support big-endian MIPS CPU; see §4.2 for a full description of the consequences. A wrongly-configured BONITO is still capable of being used by a MIPS CPU which avoids all sub-word accesses - so it's possible for your system to leave this to the default setting so long as early software changes it to match the CPU.                                                                                                                                                                                                                                                                |  |  |  |

| 13     | CPUparity   | 1 to enable per-byte parity checking; 0 to disable checks. It will not usually be necessary to set this bit from power-on. Note that BONITO always passes SDRAM parity straight through, and generates parity for I/O and PCI data.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 11     | romCs1fast  | Select "faster" operation on the ROM attached to these select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 10     | romCs0fast  | signals; slow ROM has an access time of 12 CPU clocks, while fast ROM cycles in 9 CPU clock periods. Don't change these fields while running from the affected ROM.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 9      | romCs1width | road only 1 for 16 bit POM 0 for 8 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 8      | romCs0width | read-only - 1 for 16-bit ROM, 0 for 8-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 7-6    | romBoot     | read-only - where CPU boots from; picks which memory region will be selected for accesses in MIPS' traditional 0x1FC0.0000 start address.  00 from ROM attached to ROMCS1*.  10 from ROM attached to ROMCS0*.  10 from local SDRAM. This works only if some other part of the system has filled it with appropriate MIPS code, of course; you'll start with the next value:  11 from local SDRAM; but also the MIPS CPU is held in reset until this field is changed to another value - usually "10" as above. Used for a system which expects to have software uploaded into SDRAM at power-on. |  |  |  |

| 5      | config_dis  | when set 1, BONITO responds as target to any PCI bus configuration cycle with a "retry" response. This allows your system to hold off configuration by an external PCI host while the local CPU's bootstrap software patches the standard PCI configuration registers. You should not leave this set for more than a few ms, or your host may give up on you; dangerous but useful.                                                                                                                                                                                                              |  |  |  |

| 4      | is_arbiter  | when set 1, BONITO operates as PCI arbiter. When 0, the roles of the zero-th request and grant signals are reversed, and BONITO will use the services of an external arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

#### bonPonCfg register

| Bit(s) | Name     | Value / <i>Effect</i>                                                                                                                                                                                                     |  |  |  |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3      | pcireset | If BONITO is acting as PCI bus controller (ie controlling the reset signal), this is where you can set it. A zero value asserts the active-low PCI Reset* signal; a "1" deasserts it.                                     |  |  |  |

|        |          | Note that in early specifications, this bit was used to configure BONITO as PCI bus controller. But that's now done with the dedicated signal <i>SysController*</i> .                                                     |  |  |  |

| 2-0    | CPUtype  | What kind of CPU is attached?  NEC Vr4300  NEC Vr5432  Most other compatible CPUs with wide command bus, R4000-heritage reset, and "mode bits" configuration. See §4.3.1 for where the configuration mode bits come from. |  |  |  |

Table 5.2: Fields in bonPonCfg

# 5.4. Mostly-PCI configuration - not affected by pullups

The bongencfg register brings together early-bootstrap options, but which power-up from reset to a fixed state - most often zero. Almost all of them are PCI-related.

### bonGenCfg register

| Bit(s)            | Name                | Value | Effect                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 noretrytimeout |                     | 0/1   | Normally (with this field 0), BONITO will not retry indefinitely on a locally-initiated PCI cycle where the target returns a "retry" response; eventually BONITO gives up and returns a PCI error. Sometimes the target may just be very slow, and software can catch the error condition and re-try the cycle manually. |

|                   |                     |       | Set this field 1 to disable that timeout. This risks lock-up, but makes the software simpler.                                                                                                                                                                                                                            |

| 15                | buserren            | 0/1   | Set 1 to cause any CPU-initiated PCI bus read which terminates without data to cause a MIPS "bus error" exception.                                                                                                                                                                                                       |

| 14                | mstrbyteswap        |       | Set 1 to enable the PCI byte-lane swapper for transfers between PCI and local memory or CPU, when BONITO is the PCI bus initiator (master).                                                                                                                                                                              |

|                   |                     |       | Except in bizarre circumstances and after deep thought, this should be set 1 if and only if your CPU is big-endian. Only in even more bizarre circumstances should it ever be set differently from the byteswap bit described below, which controls transfers where BONITO acts as target on the PCI bus.                |

| 13                | cachestop           | 0/1   | When 1, all PCI-initiated accesses to local memory are denied with a "retry" signal, so that the I/O buffer cache state can only be affected by CPU activity. Probably only for IOBC test code.                                                                                                                          |

| 12<br>11-10       | ciqueue<br>cachealg |       | More IOBC diagnostic fields                                                                                                                                                                                                                                                                                              |

| 9                 | wbehinden           | 0     | IOBC write-behind control Data written by a PCI initiator to BONITO's local memory is immediately forwarded to the memory controller.                                                                                                                                                                                    |

|                   |                     | 1     | Write data is retained in the IOBC until the line is recycled; much more efficient for normal purposes.                                                                                                                                                                                                                  |

| Bit(s) | Name           | Value | Effect                                                                                                                                                                                                                                                                                        |

|--------|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8      | prefetchen     | 0/1   | IOBC read prefetch control. Set 1 to allow BONITO to read ahead by a cache line. When a PCI initiator is reading a stream of data from local memory, this greatly improves performance by fetching what will probably be the next line of data from memory in parallel with the PCI transfer. |

| 7      | uncached       | 0/1   | Set 1 to enable the IOBC. 0 is for diagnostic code only.                                                                                                                                                                                                                                      |

| 6      | byteswap       | 0/1   | Set 1 to enable the PCI byte-lane swapper for transfers between PCI and local memory or CPU, when BONITO is acting as the PCI bus target (slave).  Like the mstrbyteswap bit described above, this should be set                                                                              |

|        |                |       | 1 if and only if your CPU is big-endian.                                                                                                                                                                                                                                                      |

| 5      | irqa from intl | 0     | Should BONITO's interrupt controller be connected to the PCI interrupt signal <i>INTA*</i> ?  No; <i>INTA*</i> (if an output at all), will be explicitly controlled by the MIPS CPU.                                                                                                          |

|        |                | 1     | Yes; INTA* (if set as output), will track the level from the interrupt controller (see §5.14) which is driven on the CPU's second interrupt signal, Int1*.                                                                                                                                    |

| 4      | irqa_isout     | 0/1   | 1 to drive INTA*, 0 for it to be an interrupt. It is readable as one of the input conditions of the interrupt controller, see §5.14.                                                                                                                                                          |

| 3      | force_irqa     | 0/1   | Set 1 to drive INTA* active. Note that since PCI interrupt signals are defined "open-collector" they are only in fact driven low; in the absence of any drive by any of possibly multiple connected devices a pull-up produces a high level. So the 0 value means "don't drive the signal".   |

| 2      | cpuselfreset   | 0/1   | Write a "1" to cause BONITO to cold-reset the MIPS CPU. Likely to be used only very soon after a real power-on reset, in systems where the CPU configuration is changed by software very early in bootstrap.                                                                                  |

| 1      | snoopen        | 0/1   | Set 1 to enable the IOBC to snoop uncached CPU accesses.  Sometimes helpful and usually harmless. Should normally be set.                                                                                                                                                                     |

| 0      | debugmode      | 0/1   | Powers-up to 1. Enable debug mode, in which all CPU accesses and some PCI ones become visible on an attached debug board - see §2.7. There may be some cost in performance or power, so turn this off in a system if you know no debug board will be used.                                    |

Table 5.3: Fields in bonGenCfg

# 5.5. SDRAM configuration

BONITO can be configured with a range of SDRAM memory systems. We need some standard names for talking about the chunks of SDRAM you build the system out of, and the SDRAMs themselves already have "banks" and "rows" inside. So by analogy with the DIMM modules (which many designs will use) we'll talk about *modules* each of which has one or two *sides*<sup>9</sup>. Sides can be 64- or 32-bits wide; where we

<sup>&</sup>lt;sup>9</sup> Some DIMM modules provide two chunks of DRAM all soldered to the same side of the board, while others have a single chunk of DRAM split between top and bottom; but we'd still call the chunks "sides" if they share a chip select. Sorry; we have to call them something.

want to talk about one of the 32-bit halves of a 64-bit side we'll call it a half-side.

If you solder the chips to the board then you may complain about the use of the word "module" - but it's the best we could think of.

BONITO can directly support two modules - 32- or 64-bits wide - and each may have two sides. BONITO needs to be set up so that the memory map extends from zero to the whole SDRAM system size with no holes or wrap-arounds. So the relevant parameters of the SDRAM system are:

Is there just one, or are there two modules?

And for each module:

- Is it 64- or 32-bits wide?

- Does it have one or two sides?

- How many internal banks are there in its constituent SDRAM components two or four?

- How many MuxAD addresses does the SDRAM decode in its first (Ras\*) phase? Components supported by BONITO decode between 11 and 14.

- How many MuxAD addresses does the SDRAM decode in its second (Cas\*) phase? BONITO can work with between 8 and 11.

That's quite complicated to allow for in the design, but also quite complicated for software to find out about.

By a convention initiated by IBM and sanctified by PC-100, modern DIMM modules carry "self-portrait" data encoded in a tiny on-DIMM EEROM device, accessed through a compact 2-wire interface. Software can drive BONITO's GPIO pins to access the data.

Memories built onboard or with proprietary modules will not usually have such information in EEROM - the board designer should consider how much information is needed and how software should detect any variation in DRAM types.

To complete configuration of BONITO's SDRAM controller you're also going to need some timing information, determined by your hardware design engineer, such as whether the memory array uses external registers to provide higher drive for address and control signals.

The controller can handle four physical groups of SDRAMs. But inspired by the organisation of DIMMs, BONITO's registers assume that the two sides within each module are always identically organised.

The first module's sides are selected by the signals *DCS0L\*/DCS0H\** and the second module's sides by *DCS1L\*/DCS1H\**.

Modules can be either 32/36- or 64/72-bits wide, but BONITO has only a 36-bit SDRAM data bus so wide modules are wired with the high and low data halves commoned together; transfers to wide modules are qualified by the assertion of only one of the two mask signals *DQMBLo/DQMBHi*.

BONITO always implements parity on the memory array - it passes parity through on CPU cycles, and generates/checks it on all other cycles. However, unless a 72-bit memory is set up so that half of the parity bits are always enabled with the appropriate half of the data bus (and 72-bit DIMMs don't do this) parity won't work correctly. With wide modules you can still use parity for diagnostic and test purposes - parity should be correctly stored and returned for either the lower or upper half of the normal range of this memory module, according to whether *DQMBLo* or *DQMBHi* enables the parity bits on your module.

You tell BONITO about the characteristics of each module through the register sacfg, shown in Table 5.4.

<sup>†</sup> Some SDRAM manufacturers count an internal bank-select address - the same as the BONITO signals called *DBA0-1* - into their "row" and "column" address counts, so you'll need to subtract one from those values before programming Read carefully.

### sdCfg register

| Bit(s) | Name        | Value | Effect                                                     |  |

|--------|-------------|-------|------------------------------------------------------------|--|

| 23     | dramparity  | 0/1   | Set 1 to enable parity generation/checking in the DRAM     |  |

|        |             |       | system.                                                    |  |

| 22     | dramextregs | 0/1   | Set 1 if your system uses high-drive registers to boost    |  |

|        |             |       | multiplexed addresses and shared control signals to the    |  |

|        |             |       | SDRAM modules.                                             |  |

| 21     | dramreset   | 0     | TBD - leave 0 for now                                      |  |

| 20-19  | extraswidth |       | Timing option‡                                             |  |

| 18     | extprech    |       | Timing option‡                                             |  |

| 17     | extrascas   |       | Timing option‡                                             |  |

| 16     | extrddata   |       | Timing option‡                                             |  |

|        |             |       | SDRAM shape fields - 'a' for the first module, selected by |  |

|        |             |       | DCS0L*/DCS0H*, and 'b' for the second, selected by         |  |

|        |             |       | DCS1L*/DCS1H*.                                             |  |

| 15     | bwidth64    |       | b module data width.                                       |  |

| 7      | awidth64    |       | a module data width                                        |  |

|        |             | 0     | 32 bits wide                                               |  |

|        |             | 1     | 64 bits wide                                               |  |

| 14     | babsent     | 0/1   | Set if no memory is fitted in the B module                 |  |

| 6      | aabsent     |       | Not implemented yet - ignored!                             |  |

| 13     | bsides      |       | "sides" in this module - separate bits for sides 0 and 1   |  |

| 5      | asides      |       | ·                                                          |  |

|        |             | 0     | just side 0 fitted (or none)                               |  |

|        |             | 1     | both sides fitted                                          |  |

| 12     | bbankbit    |       | No of internal banks in SDRAM components                   |  |

| 4      | abankbit    |       | ·                                                          |  |

|        |             | 0     | Two                                                        |  |

|        |             | 1     | four                                                       |  |

| 11-10  | bcolbits    |       | no of column addresses at SDRAM†                           |  |

| 3-2    | acolbits    |       |                                                            |  |

|        |             | 00    | 8                                                          |  |

|        |             | 01    | 9                                                          |  |

|        |             | 10    | 10                                                         |  |

|        |             | 11    | 11                                                         |  |

| 9-8    | browbits    |       | no of row addresses at SDRAM†                              |  |

| 1-0    | arowbits    |       |                                                            |  |

|        |             | 00    | 11                                                         |  |