Features/Q35: Difference between revisions

No edit summary |

m (fixed typo) |

||

| (One intermediate revision by one other user not shown) | |||

| Line 16: | Line 16: | ||

The main bus of the I440FX is PCI and the SuperIO chipset contains an integrated IDE controller, USB controller, and PCI-ISA bridge. The SuperIO chipset (the PIIX4) contains many common devices such as the RTC, PIT, PICs, etc. In addition, there's an special bus (X-Bus) for connecting the PC Keyboard controller and I/O APIC since these require special signals. | The main bus of the I440FX is PCI and the SuperIO chipset contains an integrated IDE controller, USB controller, and PCI-ISA bridge. The SuperIO chipset (the PIIX4) contains many common devices such as the RTC, PIT, PICs, etc. In addition, there's an special bus (X-Bus) for connecting the PC Keyboard controller and I/O APIC since these require special signals. | ||

Despite how we currently model this in QEMU, the only devices that actually exist on the ISA bus are the Serial controller, | Despite how we currently model this in QEMU, the only devices that actually exist on the ISA bus are the Serial controller, Parallel Port controller, and the Floppy controller. | ||

Compare this to the ICH9 diagram from the Intel ICH9 specification: | Compare this to the ICH9 diagram from the Intel ICH9 specification: | ||

| Line 39: | Line 39: | ||

== Status == | == Status == | ||

[[Category:Completed feature pages]] | |||

Latest revision as of 22:16, 12 September 2017

Summary

Add emulation of the ICH9 host chipset as an alternative to the current I440FX emulation. This will allow for better support of PCI-E passthrough since ICH9 uses a PCI-E bus whereas the I440FX only supports a PCI bus.

Owner

- Name: Anthony Liguori

- Email: anthony@codemonkey.ws

Challenges

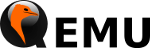

The QEMU support for the PC machine type is fairly poor today. Most platform devices are modelled as ISA devices whereas the ICH9 does not actually have an ISA bus. Below is a diagram of what the I440FX architecture looks like:

The main bus of the I440FX is PCI and the SuperIO chipset contains an integrated IDE controller, USB controller, and PCI-ISA bridge. The SuperIO chipset (the PIIX4) contains many common devices such as the RTC, PIT, PICs, etc. In addition, there's an special bus (X-Bus) for connecting the PC Keyboard controller and I/O APIC since these require special signals.

Despite how we currently model this in QEMU, the only devices that actually exist on the ISA bus are the Serial controller, Parallel Port controller, and the Floppy controller.

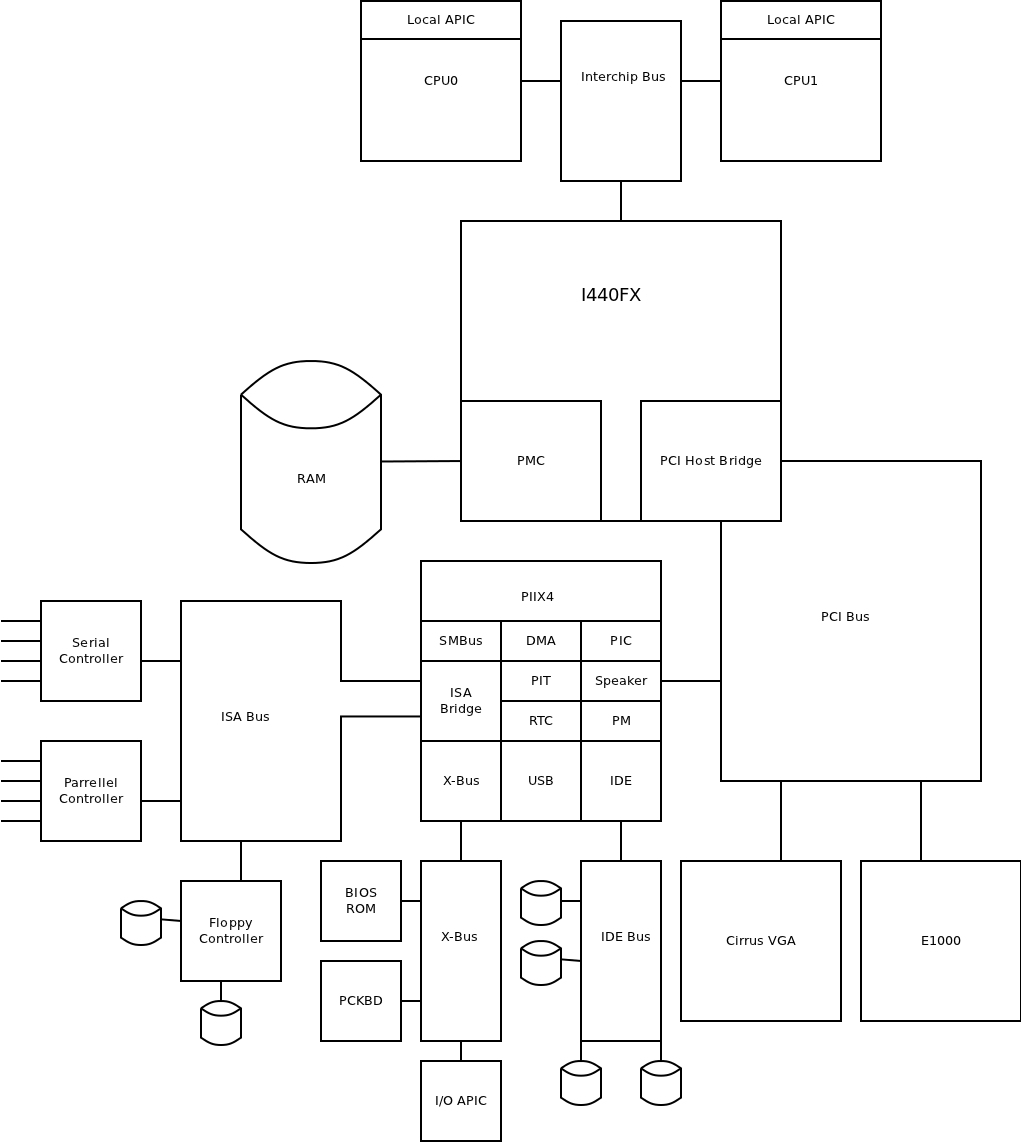

Compare this to the ICH9 diagram from the Intel ICH9 specification:

The ICH9 has an integrated AHCI controller, USB controller, network adapter, audio adapter, PCI-E and PCI bus, and LPC bus for the SuperIO devices. There is no ISA bus.

Tasks

In order to implement ICH9 support properly in QEMU, we need to teach the PC devices to not assume the existence of an ISA bus and restructure the code accordingly. Here's a brief list of tasks associated with this:

- refactor PC machine, i440fx and piix3 to take advantage of QOM

- piix3: create all child devices as proper QOM children

- Refactor i440fx to create i440fx-pmc class

- ich9: model ICH9 Super I/O chip

- ich9: make i440fx-pmc a generic PCNorthBridge class and add support for ich9 northbridge

- Refactor i440fx to create i440fx-pmc class

- ich9: implement PM interface

- ich9: introduce support for having a new machine based on the Q35 chipset

- ich9: make i440fx-pmc a generic PCNorthBridge class and add support for ich9 northbridge